ここでは遅延を考慮した場合に現れる論理素子における記憶などの概念について説明する

論理素子内部とそれを接続する線路の信号遅延は避けられないものであるが、逆にそれを積極的に利用することで記憶作用を持たせることができる。

先に紹介したアタナソフのキャパシタを用いた記憶も見方を変えれば時間的遅延要素を記憶として用いたものと考えることができる。

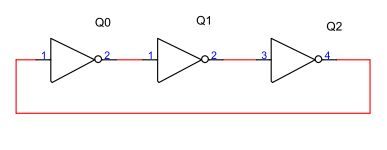

NOT回路(一般にインバータと呼ばれる)の出力を入力に接続したものを考えてみる。

これは非常に不安定なものに思えるが実際には内部と線路の遅延時間で発生するヒステリシス(履歴特性)特性のために出力信号は1又は0のいずれかに定まり、これがゲート内及び配線の遅延時間を要素として交互に反転する。

すなわち一種の発振器として動作することになる。

この発振周波数は一段のゲートと配線の遅延時間の逆数である。

実際、新しい半導体材料が作られると、その材料を用いて奇数個のNOT回路を作成して直列に接続することで、材料の遅延特性を周波数の観測から推定することが一般に行われている。

この場合には精度を高めることもあって複数個(奇数)の段数で構成するのが一般的である。

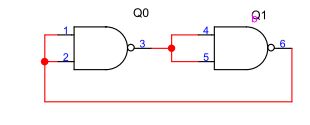

それではNOT回路2個を直列に接続するとどうなるだろうか?

これでは完全に帰還がかかった状態になって、電源が与えられると一方の出力が1、他方の出力が0の状態で完全に安定してしまう。

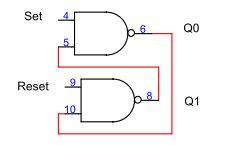

これではつまらないので両者を2入力AND回路で構成し、各NANDQ0、Q1の1個の入力Set、Resetに信号が与えられるようにしてみよう。

Setに(一時的に)0を入力するとQ0は1に、Q1は0となる。

Resetに(一時的に)0を入力するとQ0は0にQ1は1となる。

これがRSラッチ、すなわちセット・リセット型フリップフロップの基本形である。

もしA、Bともに0が入力されると後まで0である側に従うが一般には不確定とされる。

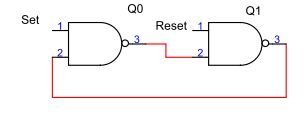

図を変形すると、良くお馴染みの形になるから判りやすいでしょう。

実際にはこのままでは不都合なこともあるので種々のバリエーションで使いやすいものにされることもあるが、これが論理回路における記憶の原型である。

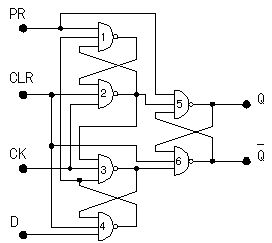

実際に用いられることの多いフリップフロップとしては以下に示すD-typeフリップフロップがある。

これはいわゆるエッジトリガータイプでクロックパルスの立下りにより動作するので入力はその時点までに安定していれば良く、また出力の変化もクロックパルスの立下りで発生

するので設計において払う注意が限定される。

(勿論クロックの立下りまでの入力の準備時間:セットアップ時間、やクロック立下りからの余裕時間:ホールド時間には注意が必要ではある。)