ここではコンピュータに用いられる論理回路と素子について解説する。

記号論理学では論理置は「真」、「偽」のいずれかの値をとり、それを処理する演算の種類も限定されている。

通常用いられるものは

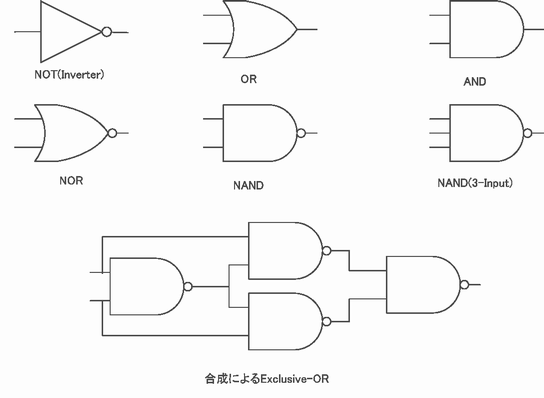

「論理和:OR」、「論理積:AND」、「否定:NOT」、「排他的論理和:ExclusiveOR」、及びその組み合わせであり、それは以下に示すの表のように表すことができる。

更に、20世紀初頭に論理学者シェファーにより、これらの演算は只一種類の演算子である「論理和の否定:OR-NOTまたはNOR」もしくは「論理積の否定:AND-NOTまたはNAND」のいずれかだけでも記述できることが示された。

合わせてNAND回路を組み合わせて構成した排他的論理和(Exclusive Or)の回路例を示す

これらはまとめて以下のような記号で表示できる

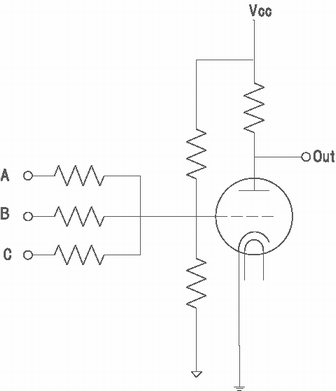

アタナソフの実際に用いた例として、真空管(三極管)と抵抗を用いての3入力NORの回路例を以下の図に示す。

図においては論理値「真」を高電位に、「偽」を低電位に定義している。3個の入力A、B、Cのいずれか1個が「真」であると三極管に電流が流れ、その結果陽極電位が低下してその出力は「偽」となる。

いずれの入力も「偽」であるときは三極管はカットオフ状態となり陽極電位は上昇して出力は「真」となる。

この回路は後にトランジスタの採用により最も簡単な論理回路RTL(抵抗・トランジスタロジック)と呼ばれるものである。

実際には入力間の分離に配慮したDTL(ダイオード・トランジスタロジック)などの改良が行われ、さらにテクノロジの進化によりMOSトランジスタを用いたもの、CMOS化で一層の電力の削減を図った回路など様々な種類が用いられるようになっている。

。

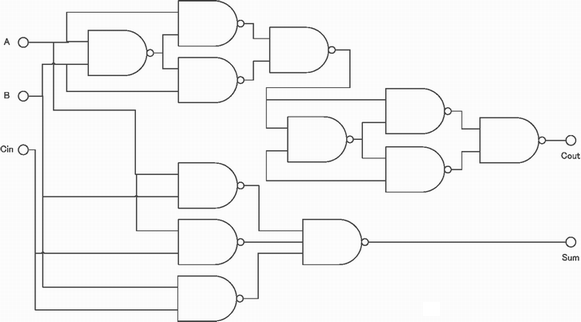

実際の回路として、全加算器の回路を以下に示す。

これは2つの入力A、Bと前の加算による桁上げ(キャリー)Cinを入力として和Sumと桁上げ出力Coutを求めるものである。

和Sumは入力A、B、Cinの1の数が奇数であるときに1となる。

桁上げCoutは入力A、B、Cinの三者のうち2個以上が1のとき1となる。

従ってその論理式は図に示すようになる。

実際にはこれと同様の機能は他の表現によっても実現可能であることは確かめられたい。

論理回路に用いる能動素子としての最初の真空管からトランジスタ、ICなど時代によりテクノロジの違いなどはあるが、一貫して性能よりも安定性と量産性を追求したものになっていることに変わりはない.

それは使用個数が膨大なものになる上、使用条件がまちまちでもあるので共通した設計条件で統一する必要があり、また環境変化、経年変化に対しても敏感でないことが要請されるためである。

例えば真空管であればあまり増幅率を欲張らず、また飽和に近い条件で使用することが望まれる。

トランジスタに於いても特別な場合を除いてカットオフと飽和の両極端での使用が行われる。

勿論高速化を目的として不飽和領域での高速動作を使用するケースも最上位機種の設計などで行われることもあるが、商用機としての観点からは例外的なものである。

特にCMOS半導体ではオン、オフの両状態では電力をほとんど消費しない特性があるのでできるだけ電力消費の大きな遷移状態の領域での動作をしないようにする設計が望ましいとされている。