目次

はじめに

1. パルス幅変調(PWM)

1.1 原理的な電力効率 100%

1.2 ノコギリ波とアナログ信号の比較で PWM はできる

1.3 素子を離れ、線型性を明示的に扱う

1.4 D 級アンプ=スイッチングによるアンプ

1.5 電力効率と PWM 周波数

1.6 無線の AM 変調

1.7 PWM 波形のフーリェ級数の構造

1.8 PWM 波形の雑音付加と除去、周期性について

1.9 デジタル PWM (離散時間系)を考えると

1.10 ON クロック期間を分散すれば

1.11 レートマルチプライヤ

2. デルタ変調(DM)から 1 bit アンプへ

2.1 デルタ変調(DM)

2.2 負帰還型 1 bit アンプ

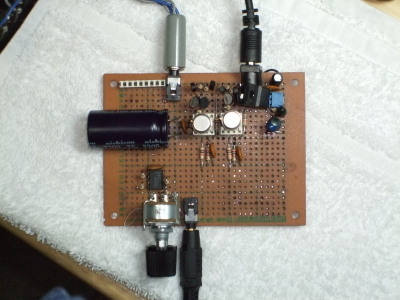

3. アナログパルス回路での初心者的 1 bit アンプの製作

3.1. NE555 を使う PWM (失敗)

3.2. コンプリメンタリ(相補性) SEPP

3.3. コンパレータとコンプリメンタリ SEPP、負帰還による 1 bit アンプ

3.4 正負2電源 1bit DC アンプ

3.5 安定化回路について、

3.6 小基板側の音量を増加

3.7 ダブルブリッジ(BTL 接続)

3.8 BTL 接続をためす

3.9 単一電源でも DC アンプが可能

3.10 2SA950/2SC2120 ペア

3.11 別基板で再度 BTL に挑戦するも、敗退

3.12 中点電位の安定化

3.13 ポリスイッチによる保護回路

4. まとめと製作上の注意

現在は、ICやトランジスタ(Tr)は、その名で検索してデータシートが入手でき、回路製作は容易になった。1 bitアンプは、最も シンプルで優れた性質をもつアンプである。その動作原理と回路の単純さは、読者を驚かせるだろうと思う。アナログアンプとの 原理的な違い、1 bit アンプのもつ特質は、音となって現われるだろう。

パルス幅変調(PWM)とは、周期的なパルスの幅(継続時間)をアナログの変調信号によって変化させることである。例えば方形波 の上側のレベルの期間をアナログ変調信号に比例させる。PWM の目的は、スイッチングを通した変調信号の再現である。PWM は、 1 周期の平均値がアナログ変調信号の1サンプルにあたり、PWM 信号自身にその変調信号を含んでいる。PWMの周波数は、低域通過 フィルタ(LPF)によって変調信号を取り出し分離できるように、変調信号に含まれる周波数より十分高くする。

なお、出力の ON/OFF による電流の変動に電源が耐えることが必要であるが、高速に変動する電流は電源に付けたコンデンサから 供給できる。また、変調する音響信号と変調される方形波パルス波形との分離のためには PWM 波形が変調信号に比べて十分周期が 短く周波数が高いことが必要である。高速なスイッチングによってこの技術は支えられているのである。

この線型性の扱いの違いがパルス幅変調(PWM)を含めた 1 bit アンプの本質的特徴であり、オーディオでは電力効率以上に重要な性質である。 アナログのリニア(線形)アンプの回路には、"リニア" という言葉に反して、素子の非線型特性に満ちている(*)。非線型特性は回路の負帰還に よって改善できるが、負帰還は副作用をもつため、全体として良好なアンプを望むには、無帰還時の本来特性が素直なものが望まれる。PWM アンプではこれを全く別の方法、レベルをスイッチングの ON/OFF 時間に置き換えることによって、線型性を明示的に扱うのである。 一般に 1 bit アンプのすっきりとした伸びやかな音の特徴は、この優れた線型性によると思われる。パルス幅変調 PWM では回路の非線型性は、 比較波形の逆関数であるが、出力波形からのLPFつき負帰還(NFB)によって動作する、後述する 1 bit アンプは比較波形の時間→電圧関数にも 依らない性質をもち、鋸波や三角波の比較波形を用意する必要もない。そしてそれはもはや PWM でさえない。その回路ではアナログ入力信号 と比較する波形は、出力パルス波形のLPF出力である。

オーディオアンプでは雑音発生源は、できるだけ避けなければならず、スイッチングは雑音源であった。そのため雑音源となるスイッチン グ電源はオーディオアンプには適さないといわれて来たが、1 bitアンプは、スイッチングによるアンプであり、それ自身、大きな雑音源 である。そのため、1 bit アンプは、雑音に強くなければそれ自身が動作できない。スイッチングが雑音になるかはその周期と周波数による。 最近のスイッチング電源はオーディオ帯域外の、オーディオ帯域より十分高域の周波数のスイッチングであり、オーディオ帯域に雑音を出す こともなく、むしろ、電力効率の観点からは 1 bit アンプにはスイッチング電源のほうがアナログ電源よりも適している。1 bit アンプは、 スイッチングによるオーディオ信号の再現であり、スイッチング電源は、スイッチングによる直流(DC)の再現であると、両者は目的も動作原 理も一致している。両方は可能なら一体化したいぐらいである。(一部の機能はすでに一体化され、NFB型の1bitアンプは電源変動を出力に出 さない性質がある。) このように 1 bit アンプは、アンプ設計の考え方を大きく変えるものであろう。

B級は、無信号時のバイアス電流を 0 にして、信号が正の半波のとき上側の素子から電流を出し下側素子はOFFにする。逆に負の半波のとき 上側はOFFにする。下側素子が電流を吸い込むように上下素子の電流(Ic1, Ic2)を、信号 x>0で Ic1= Vcc/Rl x(= 0〜Vcc/Rl)、x<0で Ic2= Vcc/Rl(-x) (= Vcc/Rl〜0)とする。電源電力 Ic1*Vcc+Ic2*Vcc は、電流が信号の絶対値 |x| に比例するので同じく|x| に比例し、 電源電力は、Vcc^2 |x|/Rl の時間平均である。信号が最大振幅の正弦波のとき、これは 2/π Vcc^2/Rlであり、最大出力 Vcc^2/2Rl の 4/π倍、このとき電力効率は π/4= 78.5%になる。コレクタ損失は最大振幅時に最大である。通常の信号波形は正弦波よりも絶対値平均が 2/πより小さく、2乗平均は 1/2 よりもっと小さいので、電力効率は、π/4 より小さい。また、信号の振幅が小さいときは電力効率は比例 的に小さい。

AB級は、バイアス電流をA級の1/πの Vcc/(2πRl) にして、小信号時にA級、大信号時にB級動作をする。両者のコレクタ損失の最小を結ぐ 切替えを最大出力の 1/π^2=約1/10にする。コレクタ損失はA級の1/π、A級動作出力の2倍、B級最大出力の 2/π^2= 20.3%である。

B級が最大78.5%の効率でも音楽のほとんどの期間である小振幅時に電力のほとんどが無駄に消費されるのに比べて、D 級は原理的には信 号の振幅によらず、つねに100%である。D級の実際の効率は、ON/OFF両レベルの特性と遷移時の特性に依存するだけである。

しかし、現在のよく設計された 1 bit アンプは例えば 95 % 以上の電力効率も不可能ではない。10W を出力する 90% のアンプの発熱 (1W)は、20W を出力する 95% のアンプの発熱と等しい。その程度の発熱なら素子に付ける放熱板は必要がなくなり、こうして、電力 効率は機器の大きさを変え、重量が10kg〜数10kg もある巨大な箱が当然であった高級なアンプは、出力トランス、電源トランス、電解 コンデンサ、放熱板をなくして小型化し、簡単に移動できる大きさと軽さ 数100g に変わる。それによって失うものがなければ、それが 良いに決まっている。いや、失うものがないだけでなく、昔の高級アンプにない恐るべき透明感をもって、すでに質的にも完全に超えた のではないかと思う。

電力効率を求めて周期内の遷移時間の比率を小さくすると、現実の素子のスイッチング速度から出力パルスの周波数には現実的な上限 ができる。現在、それは容易に数 100 kHz から数 MHz になり、すでにオーディオ帯域の上限、例えば 20kHz を十分、数十倍も超えて いるから十分であると考えるかもしれないが、高ければ高いほどよいのかもしれない。ヒトは、20kHz でなく 100kHz 程度までの音を 検知できると考えられ、求める周波数は拡大されてきた。高い周波数は、要求するスイッチング速度と電力効率に関して不利であるが、 電源コンデンサ、負帰還フィルタ、不要輻射のフィルタの単純さには有利である。

パルス幅変調(PWM)に対し、方形波のレベルを変調するのはパルス振幅変調(PAM)といい、一定幅のパルスの発生頻度を変えるのは パルス密度変調(PDM)という。PWM, PAM, PDM の波形の周波数の低域にはアナログ変調信号自身が含まれている。PWM を無線の AM に使うのは、変調信号より十分高い PWM 周波数、それよりも更に高い周波数の搬送波を PWM 波形によって ON/OFF する PWM 波形 と搬送波の積である。これから変調信号を復調するには AM 復調と LPF によって行われる。AM 復調された PWM 信号の低域に音声 信号がそのまま乗っているからである。

A(n)= ∫_0^2π f(t)cos(nt)dt= ∫_0^T cos(nt)dt= [sin(nt)]_0^T /n = T(n==0), sin(nT)/n (n!=0)

B(n)= ∫_0^2π f(t)sin(nt)dt= ∫_0^T sin(nt)dt= [-cos(nt)]_0^T /n= (1-cos(nT))/n (n!=0).

である。つまり、T= πでは A(n)= π(n==0), 0(n!=0)。B(n)= 2/n (n 奇数)。つまり、無変調の方形波には、DC分と基本周波数の 1,3,5,7... という奇数倍の周波数がそれに反比例した 2, 2/3, 2/5, 2/7 という大きさで含まれている。

T = x+π (変調信号 x) であるとき、DC 分は x+π, A(n)= sin(nT)/n, B(n)= (1-cos(nT))/n から、

√( A(n)^2 + B(n)^2 )= 1/n √(2-2cos(nT)) =2/n sin(nT/2) =2/n sin(n(x+π)/2)

PWMの n 倍高調波の振幅が Tがπを中心に揺れるに伴い sin(nT/2) によって揺れるだけである。PWMではその DC分が変調信号であり、 基本周波数の PWM 周波数は変化せず、PWM波形のフーリェ級数展開はその整数倍以外の周波数は出てこないが、それは式のもつ限界 であり、現実がそうではない。変調信号の影響による PWM 周波数の下側に側波帯もあるはずだが、この方法では表せないのである。

例えば、ふたつのPWM周期で変調信号が異なるというだけで 1/2 PWM 周波数を基本周波数にしてその全ての倍数の m/2 周波数の成分 をもつのは明らかである。n 個の PWM周期はその全ての倍数 m/n があるから、1/2 PWM 周波数〜PWM 周波数の範囲も空でない。 このように、解析よりも数値計算か実測をした方がよいと思うほど、PWM 波形はその電圧を時間に変換するという即物的な理解が 容易なのと対照的に、周波数構造の理解が難しい。

そう考えると、PWM などの1 bitアンプは、スイッチングによるパルス波形の電力増幅によって、パルス波形に含まれるアナログ変調信 号を増幅するための "必要悪的な雑音の付加" であり、加算した雑音は、変調信号から(LPF だけによって)完全に分離除去できなければ ならない。そこで、分離のためには PWM 周波数は、どの程度が必要かという問いが生まれる。PWM を情報伝送と考えると、その上側 期間を 1個ずつ読み取れば変調信号の標本値を再現できるから PWM は標本化であり、ナイキストのサンプリング(標本化)定理からいえば、 PWM周波数は変調信号に含まれる最大周波数の2倍を超えていればよいはずである。しかし、実際は分離が容易なように数十倍以上離す。 その間の違いは何か矛盾を抱えている。もともと、PWM波形は、周波数と周期をいうが完全な周期性をもたず、各周期ごとに波形が少し ずつ違う概周期性波形である。そして、重要なこととして、この周期が一定である必要はなく変動してよい。不要輻射のスペクトル拡散 のために意図的に周期を乱数で振らすこともあるぐらいである。さらに後述するが、変調信号を低域に含むパルス波形であればよいから、 1 bitアンプとしては、何ら周期性をもつ必要さえないのである。

つまり、カウンタと数値の大小比較器 (これも普通、コンパレータと呼ぶがデジタルの数値比較回路である) を使えば PWM になる。 しかし、すこし考えれば分かるように、これはそのままでは実現できないのである。例えば、仮に 16ビット精度のデジタル値を 1 の並びにするには PWM 周波数を PCM のサンプル周波数 44.1kHz とすると、その 2^16 倍のクロック、つまり 2.89 GHz が必要になる。 44.1kHzの 1/2 までの周波数しか含まない低周波信号を扱うのに、なぜ、このような論理回路としては非現実的なほど高速なクロックが 必要なのか。これは、明らかな矛盾である。そして、そもそも、何が誤りだったのだろうかと疑問を持たなければならない。

PWM 波形が AM に近似するなら、PWM 周波数の上下の近辺にパワーが集中して存在し、キャリア周波数が PWM 周波数であり、変調に よってキャリア周波数 + - 信号周波数にスペクトルをもつだろう。PWM 信号は、この考え方からみると、それら ON 期間を周期のなか で前後にまとめ、周波数を最も低域に集中させた、"最もよくない配置" の波形であり、その逆に、ON 期間をできるだけ分散した配置 というものが考えられ、存在するのである。PWM 周期内の ON 期間を分散させるシャッフルは、コンパレータへいく数値とカウンタと のいずれかを bit 逆順に接続した、並びの bit 逆順の配置である。 これは、論理設計を勉強した人にはレートマルチプライヤ(例:TTL 7497) として知られる回路である。

レートマルチプライヤは、ある意味、この矛盾の存在と解決を最も端的に示唆する回路である。その出力は、クロック 2 個で精度は 1bit、クロック 4個で精度は 2bit、8個で 3bit ..... という、精度がクロック数の対数に比例する関係をもつ。そして、最終的に レートマルチプライヤは、その bit 数からくる周期全体の ON 期間が数値に一致するという性質をもつが、そのような完全な16bitの 精度は1サンプル時間という短い期間に必要がないとすると、デジタル PWM にそれほどの高クロック周波数は必要でないことになる。

つまり、PWM 周波数の 2^n 倍のクロック周波数が必要とみるのは、周期のなかで ON 期間を前後にまとめたために起きたことであり、 ON 期間を分散させれば、PWM と同等の働きをもつ信号がずっと高周波になり得る。それによって極端に大きなクロック周波数は必要 ないし、もしかすると、サンプル周波数の数倍程度の周波数のクロックでよいかも知れない。標本値の標本毎の16ビット精度は標本毎 の独立測定だから必要であったので、2標本で 1bit、4標本で 2 bit、8標本で 3 bitという関係で、1標本が表すのはその時刻と高域 の情報、2標本はその2倍の時間と1/2の周波数の情報、n標本が n 倍の時間と 1/n の周波数に対応する情報をもてばよい。

元もと、レベルと時刻との両方の完全な標本化をもち、1/2 サンプル周波数 (fs/2) 未満の含まれるいかなる信号も再現できるとい うナイキストのサンプリング定理によって保証される PCM のサンプル毎の完全な数値精度は、オーディオ波形の再現にどの程度に 意味と必然性があったのだろうか、それ以外のサンプリング方法もあったのではないかと疑問をもってもよいのである。

しかも、過去の一定期間の平均というのは、"移動平均フィルタ" という (インパルス応答が長方形に尖っているため) 性質の優れ ない LPF のひとつでしかなく、改良できる。LPF には求める特性によって大きな設計の自由度があり、どのようにも変更できる。 過去の出力 0/1 列に対応した +1/-1 の信号に係数を乗算する LPF は係数の和と差の演算だけででき、加減算によって FIR 型の 全ての設計が可能である。これを NFB とする系は、出力を 1 bitに制限した IIR 型 デジタル フィルタと考えることができ、そ のなかで全ての過去値を和分するものがデルタ変調といえるかもしれない。

このように最初、PWM をアナログ信号の周期的波形との比較と考え、一定周期内の ON/OFF の期間による電圧の表現とみたが、そ の必要もなく、パルス波形が概周期的である必要さえない。すなわち、人間の耳、又はマイクロフォンのモデルとしてのある時間 平均(LPF出力)が入力アナログ信号を表すような 0/1 の波形を作る。それには過去の 0/1 列信号出力パターンから LPF 例えば FIRフィルタを通して様々な比較波形を作ることができる。その出力 LPF と入力信号との大小比較によって 0/1 を決めれば、PWM 周期中一様な ON クロック期間の分散でなく、PWM 周期よりも短時間に変化するそのなかのクロック単位の時刻的な情報も含み、 かつ分散したONクロック期間を実現し、そしてそれはクロックの無闇な高速性を要しないだろう。

* デルタ変調は、アナログ入力信号と出力(+1/-1)を積分した負帰還とをコンパレータで比較して行われる。音声は、これによって 2値にして通信し、受信側で積分器でアナログ信号に復号する。アナログ信号のデジタル化(符号化)の方法である。このとき時間を 離散的にするクロックがある場合とない場合がある。クロックでコンパレータ出力をラッチする(又は D-ffを通す)と、出力はクロ ック(のアクティブエッジ)時点の比較結果だけに依存してクロック期間だけ保持される。実験するとクロックが低いと音に特有の 歪が生じ、高い(例えば数MHz)と高域の伸びた音が伝達できることがわかる。クロックなしでは比較結果は素子の遅延と負帰還の伝 達関数によってループする自励発振であり、話は、より難しくなるが、クロック周期を適切に結果の1巡時間より少し長くしたもの よりも少し速いだけで類似できると思われる。製作に使うのはこの方法である。

デルタ変調は、波形の上下移動(差分)を -1/+1 に対応する 0/1 の表現をし、積分したとき波形を再現する 0/1 列を作る。負帰還経 路にある LPF を代表する積分の逆関数である微分を再現する 0/1 列を作るから、強い高域強調となって通信には使えるが、直接ス ピーカを駆動するアンプとしては(耳で積分できないので)これには向かない。そのため、完全なデルタ変調の和分(又は時間積分)は 避け、洩れのある(リーキーな)積分である "1次遅れ" がよい。それは、あるカットオフ周波数より上を -6dB/oct (オクターブ毎に 半分) で減衰させるだけで、その周波数以下にはほとんど影響を与えないという最も基本的なフィルタである。そして、この負帰還 LPF を1次遅れだけでなく最適に設計することは、問題のクロックをさほど上げないための設計と考えられる。1 bit 信号は、1 bit DA、(DA 変換というほどのものでなく、ビット電圧をそのまま音響信号にする) によってそのままアナログ信号になり、それゆえ、 アンプが直接スピーカーを駆動できるビット列を作るという条件下での LPF 設計と考えることができる。その最も単純なものは1次 遅れであり、十分高いクロックなら1次遅れでよいが、実用的なクロックでは効果的な設計があり得るのである。

オーディオ PCM サンプルのサンプル間の差分値の大きさはサンプルの絶対値の大きさよりずっと小さく、PCM よりも DPCM(差分PCM) のほうが効率的な符号化になった。オーディオ信号は、1回か2回微分してやっとスペクトルが平坦になる。これが波形の微分を符号化 する効率を説明する。DPCM は ADPCM (適応DPCM)という方向に進んだが、通常、サンプル周波数よりも大きいが極端には大きくない 周波数の 1 bit 波形でオーディオ信号は表現できる。その例がデルタ変調である。これがオーディオ信号を 16倍までで表現できる なら 16 bit PCM よりも効率的な符号化となるが、それは通常の音響では不可能であり、ここで問題にするのは符号化でないから、 これはそれより大きくてもよい。そして、これの歪の性質は、PCMとは全く異なるものであろう。数十倍のクロック (例えば 64倍で は 2.8 MHz になる)を使うことは技術的な困難以外でなく、技術的にも容易なクロック周波数である。確かにアンプの出力段のスイ ッチングは多少のパルス回路技術を要するが、我々が長い間アンプを動かしてきたアナログリニア回路よりは容易で単純であろう。

なお、製作では1次遅れをLPFにしたクロックを使わない1 bitアンプを考える。これはクロックを用意する必要がないという単純さ のためである。クロックでラッチすれば、アンプの性質はほとんど同じでも素子の速さに影響を受けにくいという利点が生まれ、 また、LPFフィルタをディジタルフィルタとして改良することが可能になる。

久ぶりにアナログパルス回路で PWM を試す。全て手持ち部品でできるだけ単純な回路を組みながら試すやり方である。最初、NE555 で試した。NE555 は、精密タイマー用 IC で直接スピーカーを駆動でき、データシートには PWM 応用も書かれている。5 V で PWM が 完全に動作すれば、AC の実効電圧が約 2V 出て 8 Ω負荷で 0.5W 近く出てよいはずである。これならヘッドフォンアンプとして 十分であり、夜用のスピーカアンプとしても使えるだろう。

(AC 実効電圧は、電源電圧 E の 1/(2√2) だから、スピーカー抵抗 R= 8 Ωは、電源電圧 E と AC 実効電力 P との間に P= E^2/(8R) = E^2/64 の関係がある。R= 8Ωでは E= 8Vで1W、12Vで 144/64=2.25 W、16Vで4W、 24Vで9W、32Vで16W、48Vで36W、64Vで64Wである。 4Ωではそれらの2倍、ダブルブリッジ(BTL接続)では、それらの 4倍になる。)

CR の負帰還の抵抗 R は上下対称デューティ 50% の波形が得られるように Out(pin3) から返す。NE555 の内部には 3つの 5k の抵抗 の直列によってふたつの閾値電圧、1/3 Vcc と、2/3 Vcc を持つ。内部フリップフロップ(FF)をそれ以下でセットする 1/3 Vcc と、 それ以上でリセットする 2/3 Vcc である。FF が 1 なら R を通して C に電流が流れこみ電圧が上昇していき、2/3 Vcc で FF が 0 になり、今度は R を通した電流は逆転し、電圧は 1/3 Vcc まで下降する。こうして FF は発振し方形波を出すが、CR の電圧と比較 する閾値 2/3 Vcc が Control Voltage (pin5) として外に出ていて信号で振らすことができる。やってみると変調度が低いようで音 が小さい。pin5 でなくCR 側に信号を結合をすると容量での結合ではその結合コンデンサへの充放電が起き、抵抗結合ではそれが R の並列抵抗として働き、C の電圧の到達目標電圧の振れ幅を電源電圧から縮め、1/3, 2/3 Vcc の (目標までの電位の 1/2 を閾値と する) 動作が違ってくるだろう。やはり、信号は pin5 に繋ぐべきだろう。

考えてみると、信号による pin 5 の電圧変動に伴って下の閾値 1/3 Vcc がその半分振れるため、下降(OFF)期間は信号によらず一定で 上昇(ON)期間だけが変化する。そのため OFF 期間は短いほうが変調度を上げる。duty 50% を諦め、PDM にするよう Discharge (pin7) を (2)(6)と結合した。(pin7 開放では誤動作する。) 前段にトランジスタ回路で増幅してみたが、それでも音量が出ない。ON >> OFF で 5V に近付き、ON<<OFF で 0 V に近付くから、つねに OFF期間 < ON期間の PDM は変調度は50%までである。期間から電圧への変 換は y= x/(x+off) の非線型関数である。OFF期間不変では、ON期間は、OFF期間の両側に変化すべきだ。つまり、OFF期間を短くしたの は誤りであった。ふたつの閾値の一方しか変えられないのがまずい。1bit アンプはデューティ比 0〜100% を目指している。NE555 の使 用を放棄する。

図(a),(b),(d) のように、上下に NPN と、PNP のトランジスタ対を使うと回路の上下対称性が得られ、上下の素子の電流増幅率(h_FE)など の特性を合わせたコンプリメンタリ(相補的)トランジスタ対を使うとさらに対称性がよい。上に PNP Tr のエミッタを電源に、下に NPN の エミッタを GNDに置く、上下がエミッタ接地の回路は、それをドライブするトランジスタが CE分割(図(b)) では、ドライバが ON のとき、 上下とも ON になる。これは逆転した別の回路と結合するときに使える回路である。ドライブ Tr がエミッタ接地(図(d))では、ドライブ 電位が Vcc/2 のとき上下がバランスし、Vcc/2 より上のとき上下が OFF/ON、下で ON/OFF の反転型になるが、上から下へ貫通する電流が あって、それは遷移時など上下がバランスした時に最大であり、しかも、それは、Vcc を上げると増えるという困った性質をもつ。

図(d)のように上下素子がエミッタ接地で、片方が他方の負荷のとき、抵抗負荷よりも電圧利得のある回路が得られる。TrのIcーVce特性は ベース電流一定のとき定電流的である。抵抗負荷は、(Vcc, 0) と (0, Vcc/Rl) とを結んだ直線を引くが、互いを負荷とするコンプリメン タリ接続ではコレクタ電流特性を左右逆にした曲線の負荷曲線をもつことになり、定電流源に定電流負荷をあてる高い電圧利得(少ないベ ース電流変化によって大きな出力電圧変化 ΔVce/ΔIb) が得られる。そして、遷移時には一方がベース電流を増やすとき他方がベース電 流を減らす。 Ibによる Ic/Vce 特性の変化が比例的にIcを変化させ、上下の素子の Tr のコレクタ電流を変化させ、Vceを大きく変え、 出力の状態が反転(スイッチ)する。

しかし、SEPP回路では出力インピーダンスの低いことが望まれるため、エミッタ接地はあまり使われず、普通、電圧増幅率が1のエミッタ フォロアを使うコンプリメンタリ・エミッタ・フォロア(CEF)が使われる(図(a))。これをスイッチングに使うとき、ベースに流し両方の素子 のコレクタ電流を決めるバイアス電流を 0 にできる。この回路は、無駄な電圧が上下に0.7V できるが、上下素子による電流 ON/OFF でなく、 基本的に変化した電圧に追従するとき電流しか流れない。ON/OFF の両状態だけでなく遷移時にドライブ電圧がどこにあっても変化しなければ、 上から下に(VccからGNDに)流れる電流がない。出力を入力変化に応じて変化させる動作に必要な電流だけが流れる。そのため、調整する必要も なく非常に広い電源電圧で動作できる。

Mos FET を使う回路でもバイポーラ Tr と同様にコンプリメンタリ・ソース・フォロア回路 (図(a)上が N-channel 下が P-channel) が 安全だが、無駄な電圧はバイポーラの上下0.7Vの1.4Vよりもさらに大きい。エンハンスメント型 FET ではソースに対するゲート電圧が 数Vの閾値以上離れないと大きな電流が流れないから、両ソース電圧は、時間をかけて両ゲート電圧に一致するが、差が小さいと電流が でないので、負荷があれば追従に時間がかかる。

上 P-channel と下 N-channel のコンプリメンタリは、ソース接地の反転型である (例:図(d))。エンハンスメント型の FET は、Vgs が ある閾値まではほとんどIdが流れず、そこからは直線的にゲート電圧の変化にほぼ比例して電流が流れるから、電源電圧が閾値の2倍以上 では上から下へ流れる電流が存在し、それはゲート電圧が中央 (Vdd/2)のとき最大になる。遷移が十分高速でそれが問題にならないなら よいが、ゆっくりした遷移や、遷移時間比率の大きいときを考えるとまずい。図(b)のCE分割は、BTL では使えるかもしれない。

上下とも N-channel の非コンプリメンタリでは下側はソース接地だが、上側はソース・フォロアである (例:図(c)のCE分割ドライブ)。 ソース・フォロアは、エミッタ・フォロアと同じく基本的機能は電圧追従であるから、上側は十分な OFF ができない。入力が high である ON と同じ状態のままゲート電圧とソース電圧が下がっているだけだから、上から下へ流れる電流がある。

Mos FET は、ソースを基準にしたゲート電圧 Vgs からドレイン電流 Id への増幅であり、熱暴走がないなど、バイポーラと比べて大電流 スイッチングに向いているが、入力容量 Cin などの容量あるためドライブ回路の負荷抵抗 R との間の時定数 t= Cin R を大きくしない ようにする必要がある。例えば Cin= 1000pF の Mos FET に R= 1kΩでは立上り時定数は t= 1μ秒になり、立下りはドライブ Tr に流れ 込むから時定数が小さいが、周期 1〜2μ秒、0.5〜1MHz以上のスイッチングはできないことになる。Cin は ON 状態への遷移では Vds が 小さくなるから Cin が増大する。順方向アドミッタンス ΔId/ΔVgs が大きく(大電流を小さい電圧変化で ON/OFF でき)、また Cin が 小さいことが望ましいが、パワーMos FETは、内部に小 Mos FET を並列に並べるだけだから、これを望むのは難しい。そこで、小信号用 バイポーラ Tr の CEF をドライブ回路として使うことがよく行われる。

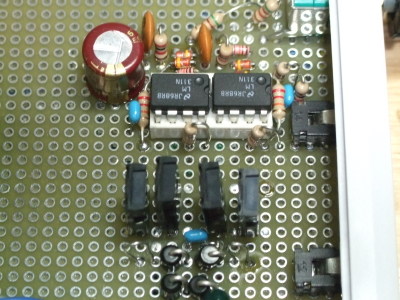

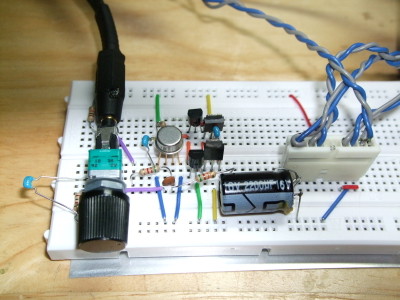

最初に成功した小基板の 1 bit アンプの片チャネルの回路を上図に示す。コンパレータ LF311 の出力 Tr をエミッタ接地で使うこと (エミッタ pin1=GND, コレクタ pin7= プルアップ抵抗 2kΩを結合) と、それにCEFをつなぎ、出力から抵抗とコンデンサの負帰還を しただけの回路である。CEF は、Tr のベースとエミッタを NPN と PNP とで結合し、NPN のコレクタは Vcc に、PNP のコレクタを GND につなぐ。そして共通のベースを入力として共通のエミッタを出力とする。これはエミッタフォロアのゲイン1の電圧増幅回路で あってインピーダンスを低くして後続の8Ωスピーカー負荷へ整合させる出力回路である。NPNとPNPとは互いを負荷にして遷移動作する。 ON/OFF の両状態で遮断、遷移時にだけ電流が流れる。両エミッタを結合した出力は、完全に上下対称であるなら両ベースの電位と一致 するが、両ベース電位を中心に +-0.7V程度の幅の制御の弱い領域をもち、入力の小さなずれは微小なベース電流しか与えず出力を動か さないため、その幅の不感帯をもつといえるだろう。

なお、CEFは、単純で安全確実な動作ができるため使う。上側の Tr である NPN は、ON 時に Vcc に出力を結合するのだが、ベースが Vcc に なってもエミッタは Vcc - 0.7V にしかならず、CE間に 0.7 V が残る。同様に下の Tr PNPは、OFF時にGNDに結合するが、ベースが GND でも GND + 0.7 である。結局、出力は、Vcc - 0.7 と GND + 0.7 の範囲しか振れないので 1.4 Vが無駄になる。ただし、その他の回路、例えば、 CE分割コンプリメンタリ・エミッタ接地(EG) (上をPNP下NPNでともにEG)などの回路(図 (b))、CE分割非コンプリメンタリ結合(コンパレータ 出力TrをCE分割し、上下ともNPNだけで上はEF、下はEG) (図(c))、などが容易なら試したいがそうではないと思う。CEFは、抵抗も使わず Tr だけで確実に動作するスイッチである。

もし、バイアス電流が必要なら両ベース間に1.4Vの電圧程度を与える回路(ベース電圧をVce の抵抗分割で与える自己バイアスTrのCE) とそれ を調整する半固定抵抗などが必要だが、ON/OFFのスイッチング用なのでバイアス電流を考えず上から下に常時流れる電流を0とする。電流制限 のために両エミッタ間に0.5Ωの抵抗を2本直列しその間を出力に使うのがアナログ回路では普通である。これは、出力のショートによる電流を 制限し、Tr の保護になるが、今回は省略した。両TrのCE間に上向きにダイオードを付ける。スピーカーとスピーカーケーブルのようなインダ クタンス(L)性負荷の電流遮断時に発生する電圧をVccとGNDの範囲に制限して Tr を保護するフライホイール・ダイオードである。

LM311 コンパレータ は、学生時代から 5 個新品を持っていた FET 入力の LF311 を使った。負帰還側は 5000pF と 2kΩであり、入力10kとの 関係でシュミットトリガ特性にする正帰還をもたせ、出力から 20K で +IN に結合していたが、この正帰還はじつに不必要だった。(OPアンプに 正帰還すればONのとき閾値が下がるヒステリシス(履歴)特性をもち、雑音に強くなる。これをシュミットトリガという。シュミットトリガ入力 に CR による1次遅れで負帰還するだけで発振回路ができる。しかし、シュミットトリガ入力でないコンパレータ入力への出力から CR の1次遅 れ負帰還だけでも十分発振するのである。)

100kHz 程度だった無音時の周波数が正帰還を外すと 1.3 MHzに高くなった。また、負帰還をコンプリメンタリトランジスタ 2SA495/2SC372 の出力側から返すと 5V で十分な音量が出た。クロックによるラッチをしないから、負帰還型 1 bit アンプは、出力からの負帰還で素子の 持つ最高速度で動作しようとする。それを途中のコンパレータ出力から帰還してしまうと、その動作が出力回路には速すぎて追い付かず、 状態遷移の動作の完了前に反対動作に入ってしまうのである。出力回路から負帰還すると全体が正常に動作する。

深夜に聞く小音量ならこれでスピーカーを鳴らすことができるが、この Tr は、30数年前の有名な小信号用コンプリメンタリTrであり、明らか に最大コレクタ電流が足りない。その目的のためには、正負の両電源を使って、入口と出口のコンデンサをなくした DC アンプにすべきだろう。

私は、テスターとディジタルマルチメータ、周波数カウンタしか持たないため、電圧と周波数をみて動作確認をするしかない。波形を見ずに 音で推測するだけでパルス回路を試作するのは、かなり苦しいが、もともと単純な回路であるから容易なはずである。音質は、出力コンデンサ が小さいので低音は不足するが非常にすっきりした高音である。1 bit アンプの基本的な機能を満たしたのであろう。

+-10V 電源で駆動するには電圧ゲインがいる。ゲインなしの抵抗分割比 1.2 のままでは前の回路と音量と音質も変わらないことを確認した。 負帰還の抵抗分割を22kΩと2kΩにする。Cは GND の間に 5000pFのまま。これで約12倍のゲインが得られ、入口に 2 連ボリューム(A型10KΩ) を付けた。配線上の注意として、GND線の最終段の大電流を敏感な入力回路の GND に流さないように分離すること。それでもVRが1/2程度のとき、 入力の信号インピーダンスが高く、回り込みが原因と思われる異常発振による雑音が残る。ラジオのチューニング時のシュルシュル音と音が割 れる感じが入力音によってときどきある。これは、浮遊容量によって帰還した異常発振だろう。また回路の入力など各部に接触したときの再生音 によって不安定さがわかる。VR の出力であるコンパレータの正入力とGND間にセラコン 102(1000pF)を付けた。 音量に不満が無くなったが、音質は、まだ前の小基板の回路を超えない。

さらに入力に 102 を追加した。信号線に入れるコンデンサはできるだけ避けたい。これは後に、コンパレータの正負両入力間の 102 ひとつに 変更し、ほぼ音が安定したので、この回路の基板をしっかりした箱 (TAKACHI MX3-11-12GS) に入れる。基板は箱の基板間口幅 100mm幅に合わせ て少し削る。入力の VR (パネル取り付け型2連VR A10K型) が箱(上空き 17mm)に入らない高さ(22mm)であったので、基板に取り付ける ALPS の 2連 VR A20kΩに変更。これに伴い、入力回路のインピーダンスが 2 倍になったことから、異常発振しやすくなり、VR から入力までをシールド 線に変更した。それでも正負両入力間の 102 は、まだ必要である。抵抗分割の値と容量の値の調整で避けられるならそうするべきだろう。

DCアンプにするための正負の2電源は、市販のACアダプターにはそういうものが一般的でなく、手持ちの AC アダプタでネジで開けられるもの (14VA, 9V出力800mA) を両波整流で 2つの電解コンデンサ(16V3300μF) に蓄える形に改造した(下図)。正負2電源(ACアダプタ出力で無音時 +-12.5V、大音量時は+-11.5V) から LM317/LM337 の可変3端子レギュレータを使う安定化回路の出力は、+9.5Vと-9.1V で振幅の必要な大音量 時に23Vから18.6Vに4.4V減ることは電力が 8.26W から 5.40W になることだから痛い。動作してから振り返ると、AC アダプタの改造によって 改造 AC アダプタから手元のアンプ本体まで 3 本線が必要であり不便なのと、正負2電源は本体に電源スイッチすら付けにくい欠点があるこ とに気が付く。

旧小基板のほう(単一電源(AC アダプタ7.5V 800mAの線直付け)、最初 5V 三端子レギュレータから、定電圧電源IC LM317に変更し 8Vに設定。 後にDCジャック (2.1mm)に変更し、LM317 は素通しにした。) で、抵抗分割を 2k,10k (ゲイン= (10+2)/10=1.2) から変更してゲイン を与える。10k, 10k にしてゲイン= 2。最初、音に影響がないように思ったが、よく聞くと高域が十分伸びていない。無音時周波数を測定すると 600kHz に下がっていた。抵抗分割の並列抵抗値が高くなって CR による時定数が大きいためであろう。必要ゲインと考え合わせ、10k,5k による ゲイン=15/5=3 にした。並列抵抗値は、3.3 kΩ。この抵抗分割がゲインと高域の伸びを決める。

しかし、これは怪しいと思い返し、注意深く聞くと、無音時にスピーカーに耳をかなり近付けたときアナログACアダプターのハム音を聞き 取ることができた。安定化回路を通すともっと小さなズルズルいう音が聞こえる。室内の他の雑音より小さければ、ハム音も雑音も違いは ないようなものだが、この後、もっと大出力に改造するとこの雑音は、もっと大きくなるだろうし、ハム音は忌み嫌われるものだから、 "ハム音など決して聞こえない現代的なアンプ" を望むなら、安定化回路は必要だろう。アンプがDCアンプになるために電源の安定化回路は 必要と思われてきたが、この回路構成ではむしろ電源安定化の必要はないのかもしれない。そして、実用的な考え方、"通常使用状態にハムが 聞こえない程度でよい"と考えるなら、安定化回路は省略できる。安定化回路は、回路全体の半分以上を占めるから、これが省略可能である ことは朗報である。さらに、スイッチングACアダプタを使う場合、すでに安定化されていて、電源ハム音が聞き取れるほど含まれることは、 恐らくないだろうから、アンプ回路の基板に安定化回路を搭載する意味は、ほとんどないと考えるべきだろう。

負帰還 1 bit アンプのオープンループゲインは、コンパレータゲインである。コンパレータは、オペアンプの飽和特性とスルーレートを改良し たものである。それはゲインのない飽和状態だけを利用する。コンパレータのゲインは理想的には無限大で、そのときにはこのアンプは電源変動 を完全に抑圧できるだろう。現実にはコンパレータのゲインは大きい(20万)が無限大でないから、理想的なコンパレータと思って使っていても オフセット電圧などが誤差として存在するし、入力振幅の小さなとき遷移が緩やかになる現象もある。この誤差、オフセットなどは、アナログ リニア回路の負帰還によるゲインの減少と線型性の向上という話とは違う話である。ここでの負帰還は、LPF を伴った負帰還である。それによって、 全体ゲインを希望の値に設定できるが、LPF を伴うから、遷移時の高速性を失うことはなく、飽和出力からの NFB は、高倍率のコンパレータ 機能を落とすこともない。コンパレータ機能には正帰還によるシュミットトリガ特性という方向も可能である。

入力波形への出力波形の LPF 出力の合わせ込みの精密さは、コンパレータのゲインと、NFB の LPF に依存する。無帰還 PWM にはオープン ループ特性(電圧→時間)があるが、PWM に負帰還を付け加えてもよい。最初から PWM のゲインを、使用するゲインに合わせる必要はない。 それより十分大きなゲインにしておき、負帰還によって合わせてよい。そのとき、PWM のノコギリ波の比較波形は、振幅を小さくし、 ほとんど平坦波形に近付き、入力波形の振幅より十分小さくなるとその周期性さえ失い、そして、この負帰還 LPF による 1 bit アンプ とほとんど同じものに移行すると考えられる。

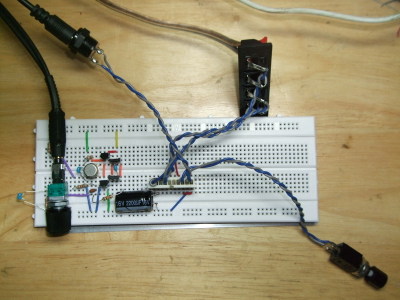

正負2電源 1 bit DC アンプを次図に示す。(後述するように、その後、コンパレータの正負入力間のクランプダイオードでさらに安定に 動作するようになった。正入力側をGNDに落とす10kΩは除去した。また、ポリスイッチ RXEF090 を正負定電圧電源の両入力側に入れた。) (さらに、(1)最大VR時の小さな白色雑音をとるため、VRから+INまでのシールド線をやめ間に直列5kΩをいれ線長の大半をVR側にした。 拾った帰還は 5kΩと+IN/-IN間の1000pFのLPFで除去される。(2)スピーカーケーブルを接続する出力端子は、ボタンを押すだけで外れる ワンタッチ式に変更した。(3)ポリスイッチ RXEF090 は保持電流が大き過ぎ取り去った。)

出力のTrをコレクタ電流が 0.8A まで耐えられる 2SA950/2SC2120 に変更して 2SA495/2SC372 ペアのそれのそばにコンプリメンタリ・エミッタ ・フォロー(CEF)を組む。回路内に多用した耐圧12V の 0.1μF セラコンを取り除き、ACアダプタからの線直付けを止めてDCジャック(2.1mm) を 付け、18V0.8A の SW型 AC アダプター(18.3V)などが付けられるように変更し、シリーズレギュレータの出力を 16V にした(後に安定化電源は 外した)。電源電圧を上げたのに伴いゲインを上げる。そうしないと電源電圧を上げた効果がない。負帰還の抵抗分割を、30k,5k にしてゲインを 7 にした。これによって小室内では十分すぎる音量になった。

ゲインを上げると異常発振しやすい。10kΩの VR であるが、やはり、VR の中途の位置でコンパレータへのインピーダンスが高いため音が 割れる現象がこの小基板でも出た。これもやはり VR 出力からコンパレータ+入力までの線をシールド線にして、コンパレータの +- 入力間に セラミックコンデンサ102(1000pF)をいれる。さらに、VRを完全にしぼったときに異常発振のシャーという音がする。すでに、電源電圧を2k2k で2分した中点電位に100μFの電解コンをいれているが、コンパレータの入力近くで、中点とGND間に 0.1μ積層セラコンをいれると消えた。 しかし、コンパレータの+-入力に導電体で接触する音に VR 最大時に怪しさが残る。異常発振が起きているかもしれない。最大音量での電源の 電流は、120mA 程度、無音時は 50mA 程度である。これならダブルブリッジ (BTL 接続) に改造しても、ACアダプターの最大電流以下だろう。

負帰還の抵抗を 5k,30k から 2k,22k に変更し、時定数15μSを 10μSに小さくすることで、LPF のカットオフ周波数を11kHz から16kHz にした。 スイッチング電源からのコネクタを接続をすると(又は出力のGNDへの接触か何かによって)、独特のプラスチックの灼ける匂いがして LED 点灯 が暗くなり、あわてて電源を外す。Trの 2SA950/2SC2120 の1組が触れないほど熱い。これらを取り外してテスターで導通を調べる。 トランジスタはダイオードの組合せと考えるの導通テストで、壊れた Tr は大抵検出できる。(NPN Trは、BからE、C へだけ導通。PNP TrはE、 CからBへの導通。) この Tr が全導通を確認して、Trを取り換え回復する。

2SA950/2SC2120ペアから戻して 2SA495/2SC372 ペアで音を出してみる。きれいな繊細な音がする。 2SA950/2SC2120 ペアとは音が違うように思う。

BTL 接続の欠点は、出力回路自体が 2 倍になることである。D級アンプでは値がデジタルであり、単純な論理反転して同じようなSEPPをもう ひとつ使うことになる。さらに BTL ではスピーカー負荷に流れる電流は正負のふたつの出力回路を直列に流れるから、出力インピーダンス が 2 倍になる。これを、スピーカー負荷の中点までの半分を負荷として正負の出力回路が動作すると考えれば出力回路にとって 4 Ω負荷 であり、出力回路から取り出す電流が 2 倍必要である。

さらに、BTL ではスピーカーの両方の線に互いに逆信号が乗り、これは不要輻射を削減させるよい面があるが、両方とも GNDでなくなるので ステレオ信号を 3本線で送れず、普通の3極ミニジャックのヘッドホンに接続できない。ヘッドホンは、BTL 接続の大出力の必要がないから スピーカーには BTL 接続、ヘッドホン用のミニジャックにはスピーカーの片方端子から与えればよい。そもそも、ミニジャックをスピーカー 出力に使うのは事故を招く危険がある。

しかし、D 級アンプは、アナログアンプと違って出力段が ON/OFF であるから単純であり、さらに出力段での消費電力が小さいので、その回 路規模を 2 倍にする BTL 接続も考慮の対象である。さらに、BTL 接続の利点は、出力コンデンサをなくすことができることである。単一電 源で DC アンプにできることは、正負 2 電源が使えない場合に重要な選択肢である。(しかし、後述するように、これは誤りだった。)

試しに動作させると、即、元のCEFのひとつの2SC2120が発熱破壊、全導通。原因は反転回路出力が常にLow(片chは、入力断線でHigh) だった。 正常に発振しないとき BTL は大電流を落とす。反転回路のベース抵抗を 100k, 10k の抵抗分割にする。出力電圧を測定すると中点電位に一 致しない。反転出力側が NFB によって制御されない場合、精度の良い BTL はできない。片CEFで音が正常に出ることを確認して同じ条件で BTLの音を聞いた。大きく伸びやかだが、異常発振が混ざり、新設の CEF が徐々に発熱し、両コレクタ間の 0.005μFのセラコンの蝋が融け るのを見て中止した。

BTL は異常発振を完全になくしてからするべきだろう。正負2電源のDCアンプもそうだが BTL は正常な NFB の制御動作がないだけで出力 Tr を壊す危険な回路である。CEFは上側の NPN Trが全導通になると下側の PNP Trも導通時に大電流が Vcc からGNDに流れ破壊が波及する。 CEFにエミッタに抵抗 0.5 Ω〜 1Ωが必要かもしれない。

BTL を止めて 2SA495/2SC372 ペアで音出し、NFB を2k,10k に変更。22kから10kにすると安定。大音量のための NFB の抵抗分割が問題だった。 コンパレータ入力は低インピーダンスであるべきで、VRの位置で動作が変わるような正入力側も低インピーダンスにすべきだろう。EFでは電圧が ずれるから OP アンプを使うべきか。それ以前に電源、GNDの配線などを安定にするよう再検討すべきだろうか。単純で容易な D 級アンプであるが 電源電圧を大きくし、NFB 比率を小さくするだけで異常発振が起きやすくなり、それを防ぐためには部品配置を慎重に検討しないといけない。 BTL は出力回路を複雑化する話であるから、BTLにする前の回路が安定でないと、とてもまともに動作しない。

スピーカーに繋がる左右の SEPP 出力のスピーカーの共通戻り線は GND である。出力のコンデンサは、なにか除去できる気がする。左右 2つの コンデンサは、スピーカーの GND 側に移動すれば共通化できる。このときコンデンサ容量を2倍にする必要はない(誤り) 。それは信号が左右和信号 になるだけであるから。この左右のスピーカーの戻り線の結合点は、中点電位に相当している。これは、正負電源の場合の GND に相当する。 単電源のときは、この中点電位が電位の基準として働くことができる。この中点電位と下の GND との間のコンデンサは実はもっと少なくてよい。 (誤り。後に 2200μF に修正した。) 低インピーダンスの出力信号が流れる経路でないからである。こうして、単電源でも出力コンデンサレス (OCL)が可能であり、入力コンデンサも中点電位を入力側の機器の GNDとすれば除去でき、信号経路上に結合コンデンサを全く介さない DCアンプ が可能である。中点電位は、最初、単にGNDとVcc の大まかな中点を与えるためのものだった。その考え方のいい加減さは発振の不安を与え、 そして実際不安定だったが、中点電位を回路全体の基準として見直して検討する。スピーカーの戻り線の左右結合を中点電位に結べば出力コンデ ンサは取り除け、単一電源 DC アンプができる。

ケミコンは 2200μFを外し、中点電位の 100μF だけに回路を変更して試す。結果は、よい。低音も出ている。これによって、BTL 接続の利点の ひとつは別の方法で乗り越えることができた。本当だろうか。中点電位は、2k, 2k の抵抗2本とGNDとの間のケミコン 100 μFである。これを スピーカーの片側に使ってドライブ能力の無さは問題にならないのだろうか。中点電位がどれだけ変動しても、それに入力信号は乗り、入力信号 の分だけを増幅してスピーカーに働く。中点電位は NFB の外である。しかし、もし、中点電位が大きく変動すると電源電圧の使える範囲が減少し 音量がでない可能性はある。要求される出力波形を満たさないなら、単に音が割れるだろう。2SA495/2SC372 ペアの音量は、和が同じ程度の正負 電源電圧の 2SA1359/2SC3422 と比べてやはりかなり小さい。取り出せる電流が小さいためだけだろうか。

その後、CEFのエミッタに抵抗 1 Ω(1/4W)を2本入れた。Ice が約 0.7Aで電流を制限するだろう。そして、OPアンプ TL072 を入力バッファにいれよう と回路変更を行った。基板上のVR中点から+入力への5cm位のシールド線と 102 を除去。OPアンプのボルテージフォロー(-入力と出力との結合)では 音の出ないモードがある。VR中点端子に接触するだけでそれが変わる。まだ異常発振が起きるようだ。22k,10K での反転2倍増幅にして試すと音が なぜか非常に小さい。スピーカー用ミニジャックの接続を中途半端な状態にしたら大きな音と発熱匂い。2SC2120 が全導通破壊し、1Ωの抵抗が灼け た。Tr が多少は保護されたと考えてよいが少なくとも 2SC2120 は壊れた。残りの Tr を組み直し利用する。

スピーカー戻りの中点電位への直結も、正常な発振がないだけで危険な回路である。エミッタ抵抗 1Ω 1/4W は保護になるがそれ自身灼け抵抗が 1/2Ωに下がる。取り換え。より耐熱の大きな抵抗を使うべきか。安全のための遮断回路が必要か。電源の電流による遮断、コンパレータのストロ ーブ機能の利用による出力 Tr の OFF 遮断、コンパレータ出力の Wired OR による ON 遮断、コンパレータの出力スイッチから一定期間(例えば 1 ms)だけ OFF である Tr との OR など色々な方法が考えられるが未定。本体回路が単純なので保護回路も単純な方法であるべきで、保護回路の 配線が異常発振の原因になってはいけない。

スピーカー戻りにコンデンサを通してGNDし、片 ch で問題ないので逆 ch を組んでそれだけをスピーカー負荷なしに動かすが発熱、発匂。分解して 調べると 2SC2120 が BE 間だけ全導通していた。導通テストは万能でない。 Tr は熱ストレスによって壊れるが導通テストが通る途中の段階がある。 プラスチックが焦げるような発熱をした Tr の再利用は無益で、それが壊れるだけでなく周囲に被害を拡大する。再利用 Trを信用せずその ch の CEF を新品 Tr にして組むと問題なかった。両 ch スピーカーの戻りをコンデンサ GND でも、中点電位直結でも問題ない。

18V 800mA の ACアダプターのDCジャックにプラグを差し込んだ途端、匂いがしてパチンと音がした。すぐに電源を外したが、みると、2SC2120 の ひとつが上下に割れ、銅板に乗ったチップが半分見えた。原因は、スピーカー用のミニジャックにミニプラグの差し込みが中途半端で左右出力が ショートしていた。それだけでこれが起きる。この 2SC2120 の導通を調べると全遮断だった。全遮断は、被害が波及しない。これを差し替え復旧。 無意味な不注意による破壊である。この Tr ペア、とくに 2SC2120 の破壊が多いが、このような激しい電流スイッチングにこれを使う事自体が 問題なのだろう。Tr は、絶対最大定格を超えればいつ破壊が起きてよいのだから、もう少し余裕のある Tr を使えばよいだけである。しかし、 この手の回路の危険性を示してくれた意味で貴重な石であった。Tr だけでなくスピーカーの保護回路を考える必要がある。余裕のある 2SA1359/2SC3422 ペアでは破壊が起きず、同じ電源電圧で動かす小信号用の古い 2SA495/2SC372 でも音量は出なかったが一度も破壊しなかった のだから、2SA950/2SC2120 ペアの性質に何か壊れやすさの原因があるのかもしれない。

TL072 に 1000pF の容量性の負荷が付いているので、誤動作の原因かとコンパレータ+入力から中点電位への10KをOPアンプからの結合に使う。 しかし、音が異常に小さい。何が問題かつかめないが OPアンプを通さずにVRから繋ぐかたちに戻す。 コンパレータの使い方として、両バランス入力(pin5,6)はすでに Vcc(pin8) に結合しているが、コンパレータ正負入力間にクランプダイオード を入れる。これは、多少効果があったようで、基板上のシールド線が除去できた。102は除去できない。

保護回路が無い状態では、この回路を改良するのは危険すぎる。結局、この回路は放棄し、Tr の導通テストをして破壊がないことを確認し、 安全確実な CEFによるシングル・ブリッジに変更する。単一電源でのDC アンプ(スピーカー戻りを 1k/1k 100μFの中間電位に結合) とした。 CEF が動作に問題がないのに比べて、この危険なコンプリメンタリエミッタ接地は、0.7V の無駄がない利点があるが、両方のブリッジから 負帰還する必要から、入力と負帰還が分離できないこと、両 LM311 の時間的ずれがあると両 LM311 が ON でスピーカー負荷と関係なしに 電源からGNDへ出力回路のTrを通して電流が流れる期間ができる危険がある。BTL 接続はこの回路ではなく、LM311から一度TTLレベルにして 反転し CEFするのがよいのではないかと思う。負帰還ループの中にTTLレベルが介在しても問題ないのではないか。とりあえず今はそれを試 みず安全なシングルに改造してその日に動作できた。前に作った正負両電源のDCアンプと比較して、若干、最大音量が小さいと感ずる。

中点電位をシリーズレギュレータを通すと無駄電力が大きく、スイッチングで出すには半分 BTL に近付き、もうひとつ出力回路が要る。 そのため、大容量コンデンサを使う。コンデンサは DC アンプにとって禁物だが、信号線にコンデンサを入れるのではないから、まだ許容範囲 と思う。しかし、この小基板の回路の音は長く聞くと疲れるのではないか、という疑いが残る。超低域の中点電位のインピーダンスが高いため 振幅制限が働くのかもしれない。小基板の1000μFを3300μFに変更した。また、異なる電圧の電源に代えるときそれに合わせて安定化回路の トリマ半固定抵抗を毎回修正するのは面倒だから、小基板の LM317 の安定化電源をバイパスさせた。このとき、音が少しきれいになったと感じた。 安定化回路も正しく動作させないと有害になり得るのかもしれない。

中点電位に2200μFをいれた単一電源 1 bit アンプ回路の片chだけを次図に示す。両chをスイッチングACアダプタ 24Vと KA350による定電圧電源 (LM317でも電流には十分余裕がある。スイッチングACアダプタに安定化されているから省略できる。)で動作する。 その後、このアンプも小基板の回路(2SA950/2SC2120で動作)と同様に安定化回路は使わずバイパスさせた。単一電源によるアンプは、様々なAC アダプタによって動作できる点が重要で、安定化回路を使うと単に電圧が下がり出力が減るだけであるから、ACアダプタの電圧に合わせて半固定 を調節する不便を避ける。このアンプで 9V 600mA DENON のトランスによるアナログACアダプタ AA-5(若松)、18V 0.8A の中国製のスイッチング AC アダプタ PSA15W-180(若松)、秋月の 24V 1.9Aの ACアダプタ (GFP451DA-2419) を試してみた。それぞれ微妙な音質の違いがあるが、全て問題無く 動作する。中点電位の耐圧 16V のコンデンサを 25V に交換すれば、この回路は、LM311の定格から 5V〜36V まで、つまり、20W(8Ω)まで基本的に そのままで動作できる。24Vでは 9W(8Ω)程度の最大出力である。

ゲインは電源電圧によらないから、電源電圧が低いと大音量でクリップ歪がでるという欠点だけで、その分、ほとんど使わない大音量を用意する 無駄な電力もない。電圧が高ければ大音量がでる。市販アンプは決してクリップ歪がでないようにゲイン設定をしているだろうが、クリップ歪を 聞くのを嫌ってゲインを小さくすると、音楽の小さい部分を拡大して聞けない欠点をもつことになる。中点電位がつねに電源電圧の1/2なら耐圧 の2倍の電源電圧に耐えられるが、中点電位が多少揺れることを考えると、コンデンサの耐圧は電源電圧の2/3程度にする。耐圧の大きい電解コン デンサは高周波特性もよいが、図体が大きい。

図には電源SW、電源LED回路を省略している。スピーカー端子には容易に着脱できるバネつきの電源用のような赤黒の4端子の"ワンタッチターミナル 4P "(Linkman WTN-21F-1274 マルツパーツ) を使った。出力ミニジャックもそのままスピーカー端子と結合し、ミニプラグの先にスピーカーケーブルを 付ける端子を繋いで、実験時に簡単に着脱できることを(誤ってヘッドホンで大音量を聞く危険よりも)優先する。回路修正の度に音を聞いて確認する 習慣がそうさせる。8cm筒型スピーカーのケーブルに圧着端子を付けてしまってから、ここからしかスピーカーは鳴らさない。別の部屋の圧着端子なし のスピーカー10cm筒型スピーカーとタンノイの同軸型には、後ろのワンタッチ端子から繋ぐ。ネジは長く繋いだままにするときにしか使いたくない。 陸軍式端子やジョンソン端子は、場所と時間をとる。最近、Integra 725 の締めると導線を捕捉するタイプのジョンソン端子に力をいれすぎて内部の ネジを外してしまった。アンプはJVCの SuperA型の A-X900と動かなくなった TRIO KA9300をもつ。それらと比べてこのアンプの透明さをはっきり確認 でき、"我々は今まで何をしてきたのか" と言えることが私にとって最もうれしいのである。

また、正負2電源型のアンプにコンパレータの正負入力間のクランプダイオードを入れてなかったのを入れた。コンパレータ正入力側の GND へ 落としていた 10KΩは無くす。正負入力間の1000pFとVRから正入力へシールド線を使っているのにアンプのケースに触れると小さいシャーという 雑音が出没するような状態は直り、より安定的に動作し、音はより明確になった。

また、このアンプも最後にLM317/LM337を使う安定化回路をバイパスさせた。前述のように、改造アナログ AC アダプタ電源ではハム音を聞き取る ことができ、それは、耳をスピーカコーンから数cm以内に近付いたとき可能な程度である。しかし、それよりも安定化回路によって正負の両方の 電圧からそれぞれ2、3V取られる損失の方が大きい。安定化回路は、電圧可変型の3端子レギュレータの簡単なものだったが、出力ショート時の 発熱が大きくここにだけ(出力のSEPPには付けない)放熱板を付ける必要もあった。出力回路の電流が過大で電圧が安定して出せないとき、電圧降下 の全てはLM317/LM337にかかってしまう。放熱板には銅板や真鍮板の工作より、適度な大きさで工作量が少ないことから、東急ハンズで買った鉄板 の連結金具を使った。音質は、むしろ安定化回路がない方が好ましいようだ。基本的にはどのようなものも、多少は音に影響するから、余計な回路 はないほうがよい。安定化回路が無くなれば回路は数cm平方のなかに収まるようになり、この箱でさえかなり大き過ぎる感がする。

私にとって 1 bit アンプは、学生時代にやり残し、間の30年近く放っていたテーマの復活であり作業の継続であった。金田明彦氏の DC アンプの本は、 当時、私の到達できない先にあった。1985 年仕事をするようになり生活が変わってから、時間をオーディオに割くことはできなかった。この間に世界 は、徐々に 1 bit アンプの時代に入っていた。私はこの動きを知ってやり残した宿題を思いだした。私は、確かにこの動きの端をつかんでいた。そし てそれを離したのである。1 bit アンプの素晴らしい原理と単純な回路は、恐らく当時から多くのオーディオ技術者が夢想し、工夫を積み重ねてきた ものである。そして、もちろん、ここで紹介したクロックのなしの負帰還型以外の 1 bit アンプがある。無帰還 PWM 型、PWM+負帰還、クロック付き 負帰還、ディジタル演算型負帰還型など、それぞれに得失があると思われる。どれが最終的になるかは知らない。しかし、人々がこのしくみを知って から後は、1 bit アンプはアンプの標準回路として定着しそれ以外のアナログアンプは、真空管アンプのようにそれを好む人だけのものになるだろう。 それは嘆く必要なくむしろ喜ぶべきことである。これは技術の正常な姿、全ての過去を無意味にしていく自己否定である。私には全ての過去の記憶が ある。そして、物持ちのよい私の部屋の隅に高校時代の50W+50Wの巨大な出力トランスと電源トランスの乗った6L6GCプッシュプルのシャーシがある。 埃と少しばかりのその後の修正を行ったその箱は、少なくとも当時の私にこのような単純な回路を夢想できなかった証拠である。私はそれがうれしい。

当時できなかった理由は、そのような事ではない。恥ずかしげもなく弁明すれば、高品質オーディオをスイッチングで実現することが可能と私の周りに 示す兆候は、いま信じられないかもしれないが、全く何もなかったのである。今回の一連の実験は、それが可能であることを私はすでに知っていた。 それが一番違うのである。あることが可能であるというのは最高の情報である。それがないだけで、だれも試そうとも思わない。人々はどれだけの 回り道をするだろうか。発明とか発見とかいうものの偉大さはそこにある。1972年にPWMによるアンプを実験しても音質は特によいわけでもなかった。 オシロでみると横に揺れる方形波の縦線だけでなく肩の一部が波打って縦にも揺れていた。その場である先生がそのことを指摘されたのに私はそれさえ 直せば音質がとび抜けるとは決して予想しなかった。その先生もそうだったろう。私は単に正確でない波形による発表への否定的な意見と受け取って しまった。そのような誤りが、大事なことを見えなくさせる。

私が学生として習った信号解析の数学程度では PWM を扱うことは困難だった。私の当時の基本的な技術の思考は、グランドなしの 1 本線に信号を 伝えることはできないかとか、グランド付きの1本線に 2bit 以上のパルスを乗せることができないかという多レベルの利用であったり、ある瞬間に パルス信号があることの情報によってひとつのパルスに乗せる情報量はいくらでも増やせるのではないか、などの時刻の利用であった。1パルスが1bit の情報量に対応しないという考えに取り付かれていた。そして、私の発した質問は、"1 bit信号で表せる波形は、多bit信号で表せる波形と違うかどうか" という問いだった。私の先生は即座に "それは最初から明らかだ、多bit は1bitを含んでいるから、多bit の方が広いに決まっている" という答えであった。 この答えの正否についてしばし措き、実際、私は反論をしなかった。この問は、豊かな 1 bit 波形の技術の背景と周辺の知識の不足を感じた私に 永い熟考の時間を与えてくれた。当時は、この答えにさえ、反論する材料は、何ひとつなかった。そのことの恐ろしさを今、思い出す。

(1) 入出力の分離。コンパレータ出力以降の出力回路とコンパレータ入力回路とはそれぞれできるだけコンパクトに配置し、遠ざける。 その間にはコンパレータと負帰還抵抗だけがある。入力は、ミニジャックから入力しボリューム(VR) の前に増幅しない。作るのは メインアンプだけであるが、VR は、省略できない。このような高雑音では易しいはずの OPアンプも容易に動作しない。VR は、 低インピーダンスが容易である。ステレオ用の2連VRは A 型 10kΩか、20kΩまでにする。VR からコンパレータ正入力への線は 数 cm でもシールド線が必要かも知れないが、シールド線は音に影響しそうだから避けたい。

(2) 出力回路のGNDに流れる電流を入力回路のGNDに流さないよう両者の線を分離する。出力回路の電源とGNDに流れる電流の回りかたを 意識し、離れた部品間の浮遊容量による電圧帰還を警戒するだけでなくGND線に乗る電流からの帰還を警戒する。

(3) コンパレータ LM311 は高速動作するように LM311 の両方のバランス端子(pin5,6)をVcc(pin8)に結合し、正負入力間(pin2,3) には、小信号用ダイオード2本を逆向き並列したクランプダイオード、必要最小限のコンデンサ(1000pFまで) を安定動作のために使う。

安定化電源回路は必須でないが、あると両者を比較できる。ダブルブリッジ(BTL)は成功していない。スイッチング素子としてバイポーラ より一般的な Mos FET も使っていない。自分で使うアンプにはこれで音量不足を感じることはないが、広い部屋で鳴らす場合などもっと 音量が要る場合、電源電圧を 2 倍に上げ、又は ACアダプタをふたつ使えばその音量は得られる。しかし、同じ回路でも低い電源電圧で 動かすと帰還抵抗比を大きくでき容易に動作できる。最初から大電力を望んでも安定動作は難しく、成功するには音質を確認しながら 改善を繰り返すことが必要であろう。

ユニバーサル基板上に配置を決め半田付け配線した。半田はスズ60%鉛40%。Pbフリーはこの手の試作には向かない。昔のAntexの半田鏝から 20Wの半田鏝に変更し、机にビニールテープで固定した水を湿らせた海綿付き小さな半田鏝台、小さな精密ドライバと安ピンセット、机上で 基板が滑らないように敷くタオルは有効だった。電源とGND線はニッケルメッキ線か0.5mmの架橋ポリエチレン被覆単線。信号には0.3mm被覆単線。 昔はより線を使ったが、被覆によっては熱による崩れが多く、今回の単線のほうが配線は容易である。細い単線は、半田付け後に線の向き を変えるだけで切れることがある。ガラスエポキシのスルーホール基板は、美しく力学的に堅牢な回路を作ることができ、表面だけでの 配線もできるが、配線変更時の部品の抜き取りが半田吸収線だけでは難しい。

この試作記 (Tr 破壊記?) は、初心者を恐がらせるためではない。初心者ほど勇気があって少々のTr破壊程度では恐れないのを感じて頂きたい。 複雑な保護回路、ヒューズだらけの回路を嫌うのは、それの動作が理解できないし、予想どおりにいかないからだと思う。回路の素晴らしさは 個別部品で存在しない機能が生まれ、その動作原理を理解できることである。単純な回路であればあるほど、それは素晴らしい。シンプルな構成、 組み合わせはそれ自身が美であり、動作はそれに伴う働きである。シンプルさは機能美をもつ。構成のもつ機能を引き出すには余計なものを除く ことから始めなければならない。よい保護回路ができれば追加掲載する。

人体に不要電波輻射がどう影響するかは不明であるが、この回路製作途中で耳鳴りがして気分が落ちることが多かった。恐らくは、大音量で テストして聞くと耳鳴りするのは当然で、血圧が原因かも知れない。電磁波輻射によるものではないと思うが、FCC の基準を満たすには出力 にLC回路によるフィルタが要るだろう。それもできれば追加掲載したい。 (42kB 3/16 2009)

セメント抵抗20Wの8.2Ωと3.9Ω(TAKMAN)各2個を千石電商から購入し、8Ωのセメント抵抗を左右のスピーカーの代わりに端子に繋いだ。単一電源型 1 bit アンプを18V 0.8A のスイッチングACアダプタにつなぎ、電源 SW の OFF のときの端子間にデジタルマルチメータの10A測定端子を繋ごうとする。 電源電流の測定は、OFF にした電源 SW 端子間を使えば回路加工なくできる。デジタルマルチメータにつなぐのに2本のミノムシクリップ線は必要で、 電源SWの端子間で両ミノムシクリップが互いに接触しないように紙を挟む。最後にデジタルマルチメータとミノムシクリップの線の片側を繋ぎ回路を 閉じて数秒で電流値を読みとる。

無音時の電源電流は、0.56A である。抵抗負荷の電源電流は大きい。スピーカケーブルとスピーカーは、インダクタンスによって周波数に比例 する高いインピーダンスをもっていた。抵抗だけではSEPPの上側がON時は、電源電圧18V と中点電位9Vとの差9V-0.7V を約8Vとして、8V/8Ω=1A の電流が負荷を通して中点電位に流れ、OFF時には中点電位のコンデンサから、負荷8Ωを通してGNDに 8V/8Ω=1Aの電流が流れる。上下の導通は 同時でなく1/2の期間に分割されるから平均電流は0.5Aである。残りの0.06A は抵抗、コンパレータなどに常時流れる電流であろう。こう説明が 付くように思ったが、じつはステレオでこの2倍の1Aでなければならないことに気が付く。いずれにしても、セメント抵抗負荷での電源電流測定は、 スピーカー負荷と全く違う結果になり、スピーカーの代わりにならない。スピーカーのインダクタンス程度のLを直列にいれれば結果は合うだろうが、 その測定の意味は疑わしく通常時に余分なLである。不要輻射防止のためのLCフィルタには意味がある。

LM317のような可変電圧3端子レギュレータによる電流の制限は、図15(a) のように、直列抵抗 Rs を出力にいれ、Rs と出力電流による発生電圧が 1.25V の中にある場合、出力電圧Vo、出力電流Io を使って、

Rs Io + Vo/k= 1.25V, 1/k= R1/(R1+R2)

という関係があり、例えば 25V 出力する場合、k= 20、12.5Vで k= 10。これから、

Vo= k (1.25 - Rs Io)

Vo には抵抗 Rsの k倍の電圧降下がある。電圧降下は線形で、ある電流を超えると電圧を0にしたいという目的を果たさない。図15(b)は、GND線を 戻る電流にRsをいれ、TrのBE間にして Rs*Io が0.6V以上でTrがONになり Adj端子を下に引き、出力電圧を1.25Vまで下げる。0.6Vの無駄電圧があるが、 電流遮断になりそうだ。これは、(c)のように、Trの EFでもでき、(d)は、上側では clump TrがNPN EFのベース電流をバイパスし出力を電流制限する。

スイッチング電源は、本来ON/OFF動作で異常時に電源を遮断でき、スイッチングACアダプタには大抵、電流遮断の保護回路が付いていると期待する。 そのとき電流制限では大電流が大電圧のまま電源で消費されるから考えられず、電流遮断でないはずはない。電流容量が適切ならスイッチングACアダプタの 保護回路を利用すればよく、それ以外の保護回路は要らない。しかし、それは電流容量までは出し続けるし、我々は大きめの電流容量のアダプタを買 うものである。また、ACアダプタの交換を考えれば、その保護回路を期待して全く対策を考えないわけにもいかない。単純でよい方法があればである。 保護条件には電源又は出力の過大電流と出力のDC電圧であり、保護する手段は、電源の遮断が適切であろう。

DCアンプには DC検出による保護回路が使われる(図15)。状態を保持するのは NAND 2 個を互い違いに出力から入力へ帰還する RS-FF である。 左右出力のCenterとの差のDCが0.7V以上を検出して~Sでセットし、電源ONの遅延立上りで~Rでリセットする。保護状態から復帰するには電源をOFF/ON する。RS-FFは、~S,~Rの両方がLowのとき両NAND出力がHighだから~S側のNANDの出力を保護に使えば~S~R同時にLowのときも保護するよう、電源ONによ るリセットより保護条件を優先する。遮断には電源電圧を低下させるか、電源に直列した素子をOFFにする。例えば、LM317のadj端子をGNDに導通すれ ば出力電圧を1.25Vまで下げられる。なお保護回路の電源は遮断前から取る必要がある。遮断用の素子は、電源ICやTrよりMos FETが正常時の電圧降下 が少ない。LM317では2.5V(12Vで20%、24Vで10%になる)消費する。低損失電源ICやTrでも0.6Vだが、Mos FETなら0に近い。出力回路の下側のN-chのGS間 へWired ORすると下側をOFFできる。しかしまだ保護回路は複雑で、その必要性に疑問が残る。

ポリスイッチは、回路の過電流を検知してその場で遮断する素子である。遮断が速いなら他の保護回路は不要になる。速く反応させるには小さめの保持 電流を使い、使用時の最大電流程度を保持電流にする(周囲温度40°Cを考えて1.2倍とレイケムの資料にある)。ただ、小さい保持電流のポリスイッチの抵 抗は大きく、回路への影響を考慮する必要がある。テスターでポリスイッチの抵抗を測ると0.4A型で0.6Ω、0.5Aで0.5Ω、0.65Aで0.3Ω程度、0.75Aで 0.25Ω(*) である。保持電流の電圧降下は、0.2〜0.25Vであり、まだ受け入れられる。

スピーカー出力端子保護は、熱で抵抗を上げる小型電球やヒューズが使われた。出力の遮断は、出力回路の貫通電流を防げないが、事故のほとんどが出力 ショートだから意味がある。左右出力に各1個のポリスイッチを入れるとき、負帰還ループ内なら特性への影響が少ないからそうしたい。スピーカー線の 戻りなら1個ですむが、負帰還ループの外であり音が外に拡がるだろう。8Ωのとき保持電流0.5(0.65)Aは2(3.4)Wであり、2倍の電流は4倍の電力、8(13.5) Wで遮断になる。フォステクスの8cmのFE83ユニットは定常2W最大7W、10cmのFE103は、定常5W最大15Wだから、スピーカー保護用は、FE83には 0.5A、FE103は 0.65Aが適切である。しかし、繋がっているスピーカーを知り得ないアンプは、その最大出力電流で制限するしかない。24(16)V電源のシングルブリッジ8Ω 負荷の最大出力、9(4)Wは、1.1(0.75)Aの出力電流であるが、音楽ではその電流は数秒も持続しないとすると、スピーカー端子のポリスイッチの保持電流は、 その半分の0.65又は0.5(0.4)Aの保持電流でよい。

電源での遮断は、最大出力9(4)Wは、電源 24V の 0.375A (16V 0.25A)にあたる。両ch分で2倍、保持電流で1/2して元に戻り、0.4A(0.25A)でよい。AC アダプタの電流容量は左右最大出力には正弦波形1周期の瞬時値として24Vでは0.75A(16Vでは0.5A)必要である。その数秒分の電流の電荷を貯められる ならその半分にできるが、1Aの電流の1秒間1Cを1Vの変動で出入するには1Fの容量がいる。(電気二重層コンデンサは通常2.5Vで、24V電源にいれるには 10個直列、10Fの1個300円の部品10個はまだ他の部品全体より高い。) 電源遮断のポリスイッチの保持電流が出力端子の値より小さいのは、電圧が約3倍 違うからである。ここでアンプは電圧の変換をしている。出力端子での最大波形は電源電圧の1/2√2=約1/3である。電源ポリスイッチの保持電流は、 出力端子のそれの2/3程度以下でよい。

異常な大音量に人は VRを下げるが、DCは、スピーカコーンの動きを見ないと音だけでは気が付かないことがあるし、DCアンプにはDCによる保護回路 が重要だった。DC検出回路は、0.数秒のDCの積分で反応できる。アナログACアダプタでは異常な大電流による電源低下を(一方の出力をショートした とき他方のスピーカーからの)、ハム音で気が付くことができる。しかし一般に出力ショート時、音がしないで気が付き(さらにVRを動かして)、電源を 落とす。大音量や基板試作中の匂いよりも気が付くのに時間がかかる。その場合、ポリスイッチに数秒での反応を期待するには保持電流の5倍の電流 を要する(0.5Aは2.5Aで4s、0.65Aは3.25Aで5.3s 0.75Aは3.75Aで 6.3s)。大音量音楽の実測(単一電源型18Vで0.23A)から、18Vで 0.2A(24Vなら 0.3A) に保持電流を選べば1(1.5)Aで数秒で遮断できる。

((*)ポリスイッチの資料(レイケムサーキットプロテクション)に代表値としてあるのは、RXEF 72Vでは、 0.2A 2.29Ω、 0.25A 1.60Ω、 0.30A 1.11Ω、 0.40A 0.71Ω、 0.50A 0.64Ω、0.65A 0.40Ω、0.75A 0.325Ω、 0.90A 0.255Ω、1.10A 0.200Ω、 1.35A 0.155Ω、 1.60A 0.115Ω、 1.85A 0.1Ω、 2.50A 0.065Ω、3.00A 0.050Ω、 3.75A 0.040Ωである。)

ON/OFF のドライブ波形は、素子が十分高速であればON/OFF間の遷移の詳細を考える必要はないが、その短い遷移時間の比率が高いような周波数で動作 させるとき、この遷移時の上下の素子のON/OFFが同時でないことを考慮しなければならなくなる。上がONのとき必ず下の素子がOFFになればよいが、 遷移途中に上下ともONとなる期間があれば、そのとき電源からGNDに上下素子を通して貫通する電流が存在する。それを避けるために、上下素子の動作 時刻を違え時間で分離し、他方が確実にOFFになる時間だけ待ってからONにする休止期間制御がよく使われる。それには、このドライブ波形とそれを 遅延した波形との論理積で下の素子のゲート電位をドライブし、両者の論理和で上の素子のゲート電位をドライブすればよい。上の素子のゲート電位は、 下の素子のゲート電位より速く high になり、遅く low になる。こうして上下同時 ON による貫通電流が避けられるのである。

しかし、この時間による方法は、レベルの問題を時間で解決するのであり、1 bit アンプにさらに別のレベルの問題を持込むことになり、クロックを 持たない素子の最高速で動作する負帰還型の 1 bit アンプでは設計を難しくさせる。遅延による排他制御は、相手側がOFFであるという確認でなく、 相手側がOFFになるだろうという時間だけ待つだけであり、遅延は、多くの要因に依存する素子の遷移時間の最大以上に設定する必要があり、それは つねに余分な遅延を意味し、素子の最高速度での動作を妨げる。貫通電流を回避するには、他方がOFFでないとONにならないという論理による排他制御 がよいと思われる。以下は、その考え方に沿った設計経過であり、途中、誤りに入り込むことも記述するので、そのまま回路製作を試そうとされる人に はお薦めしない。

エンハンスメント型 Mos FET では、ゲートソース間電位Vgsが閾値Vtを超えたときドレイン電流Idが閾値を超えた分の電圧にほぼ比例する(Id∝Vgs-Vt)。 そのため、コンプリメンタリ・ソース接地(図14.(a))では電源電圧Vddが閾値Vtの2倍までは突入電流が小さい。Vdd= 2Vt では入力電位が中央のとき、 突入電流は小さな値(例えば1mA)である。Vdd がそれより大きいと貫通電流は大きくなる(同図(b))。これを防ぐには、Vzd= Vdd-2Vt であるツェナー ダイオードZDを使って電源電圧の一部の電位を固定して取り去るレベルシフタを使う(同図(c))。そしてZDにCを並列することもよく行われる。抵抗 R に掛かる電圧は、Mos FET のON電位4-5V程度に小さくでき、CからZDを通した放電が少ない点もよい。両ゲート間がZDによって結合され低インピーダンス である。しかし、この回路の欠点は、Vdd に応じて Vzd が決まるから、ZDを決定後 Vdd は変えられないことである。

コンパレータ出力TrのON時に1kと270Ω直列に電流が流れ、電源電圧Vddが分割され上側のP-chのGS間は-3VになりON、下側のN-chはGS間が ほぼ0VでOFFである。出力TrがOFFになると VpとVnは、1kの両側の電圧を保持したまま 4V 上昇し、下側の N-chのGS間が4Vまで上りON、上側の P-chのGS間は0V以上になりOFFになる。問題は Tr ON時の下のOFFは確かとしても Tr OFF時に上側OFFが確実かどうかであるが、コンデンサの電荷 が全て抜けると(Vdd-4)*0.27/1.27 は 2V程度ありOFFとは言えない。しかし、TrがOFF時のCRの時定数は 1k*5nF=5μSであり、しかも、1kの両側 の電圧、Vp-VnはVdd*1k/1.27k からそれより少し小さい電圧 (Vdd-4)*1k/1.27k を目指して変化するだけである。電源が 16V ではこれはTrON 時の3/4である。半周期が0.5μSとすると2.5%程度の変化であり、ほぼ保持される。Tr ON時には、その電位からの充電が270Ωを通してされる。

最初、コンデンサが充電されていないとき、コンパレータ出力TrがONである間、270Ωを通した時定数270*5nF=1.2μSでの充電がされる、その間、 上側P-chがONであり、コンデンサ電位が十分でないときTrをOFFにすると下側N-chもON、上下が ONで電流が貫通する。そのため電源ONから数μS 程度、TrをONに保つ必要があるが、これは、自動的に満たされていると思う。Mos FETの出力回路は、ソース接地の反転型だから、コンパレータ の+IN側に負帰還の抵抗分割が付き、コンデンサが+INとGND(それは中点電位だが、-INの基準でもあるからそれは関係しない)との間にある。この コンデンサへの充電の時間(時定数、1k*5nF=5μS) の間、コンパレータ出力Trは出力をLowにするONを出す。問題の出力回路のCR時定数は、それより 短いため、出力回路のコンデンサへの充電中にTrはOFFにならず、貫通電流は流れないようだ。しかし、保護回路からTrONへの制御を付けるのが安心 かもしれない。

コンパレータには LM311と比べて2倍ほど高速なLM319を使う。LM319の絶対最大定格には問題があり、GND(LM319出力Trのエミッタ)とV++の間が最大 18Vとあり、GNDをV--にすると電源全体が18Vに制限される。しかし、最初はそれでやってみる。cut & try(設計をやめ実験)である。ZDはあり合わせ の4.2V と3.7Vの2本。基板ができても迷い、2日目に電気を入れる。激しい発熱。すぐに触って火傷するような温度で電源SWを切る。ZDが上側の素子 のOFFを妨げることに気が付き、ZDとコンデンサを外して、基板が汚くなったのを気にせず、今度はFETに触ったまま電気を入れる。 やはり発熱。1回目ほどではないが、すぐに熱を感じ止める。

やはり、遅延と論理(下側はAND上側はOR)による上下ともOFFの休止期間が必要かと考える。上下のゲートに直接に結合可能なのはCMOSであり、その 電源最大がやはり18Vという問題がある。4049のNOT4個による遅延は小さいわりに4001の論理の部分の遅延が大きい。CMOSの遅延は電源電圧によって 大きく変わる。そしてこの場合、必要な遅延と実際の遅延が明確でないことが問題である。遅延が数100nSより大きいと Tr よりクロックが低下し Mos FET を使うメリットがないだろう。Trのコンプリメンタリ・エミッタ・フォロアを超えることは難しい。0.6Vx2の無駄は、24Vからは 5%である。 その5%のために CMOS IC を数個も使うのは敗北的である。とはいえ、単純なコンプリメンタリ・ソース・フォロアでは Trの3倍、4Vもの無駄が出る。

レベルの問題は、遅延によらずレベルで解決したい。P-ch は Vdd と抵抗分割で電位を内分し、N-ch は GND と内分して両ゲート電位を与えれば、 Vtを実質、拡大するが、比例的に拡大しても2Vt>Von にはならない。また、ZDを使って変動範囲を狭めてもVddが Vdd-Vzdになるだけで、2Vt>Vdd-Vzd =Vonでないと貫通が残るだろう。0とVddの外側の電位に引っ張れば両方ONを避けられるが、電源が複雑になる。結局、LM319の出力電位が0〜Vddの範囲 を反転写像して上下素子ともONが起きないようにすればよいと考えた。これは、TrのE接地による反転によってできる。LM319出力を下はNPNで反転し、 上はPNPで反転して各ゲートに与え、コンパレータ出力電圧の0〜Vddの中央で上下ともONだったのを、中央はOFF、周辺の上下でそれぞれONにする。 このTr(2SA1015/2SC1815)は、両方ONになるが両方OFFにはならないので負荷を共通にできる(図16(d))。後段のMosFETはその反対に両方OFFにはなるが 両方ONにはならない。

最終の図16(d)の回路は、TrのCEFと比べ反転用Tr2個と抵抗4本が余分に必要となった。TrとMosFETとの音質の違いはないと予想したが違った。 (1)全く音の出ないモードがあること。何かのきっかけで音が出たり出なかったりする。 (2)VRが小さい位置で音が歪む。低インピーダンス入力時の 異常発振のようだ。負帰還抵抗が10k+1kであり、入力VRが10kであるから、基準である中点電位の強度不足(インピーダンス高)を疑い 抵抗分割1k+1k に各1k並列したが効果がない。測れば出力電圧と中点電位がともに0V近辺である。(1)は、負帰還があるのにそれが安定するのは出力が中点電位より 下がれないことのようだ。負荷であるスピーカー線を外して電源ONすれば出ない。電源ON時に中点電位が低いままだとこの状態に入るようだ。中点電位 が中点を保って立ち上がるよう、電源と中点間に中点GND間と等容量のケミコンを付けて解決した。それに従って電源ON/OFF時の異音も消えた。 電圧を反転する回路は電源電圧の影響を受けやすいから、このような電源ON/OFF時の問題が起きる。

(2)の問題には中点電位と電源,GNDの両者の間にコンパレータ入力近辺とセラコン付近の両方に積層セラコン0.1μF を入れる。今度は、VR位置が極小 のときの入力音に伴う雑音と VR 最大付近の白色雑音が残った。これも低入力インピーダンスが原因で、VRとコンパレータ+INの間に抵抗2kを入れてみ て解決した。クランプダイオードが正常に+-0.6V以外を制限するのに必要な直列抵抗が、-IN 側は負帰還1k+10kの抵抗分割で900Ω、+IN 側がVR位置 最大最小付近で小さすぎ、和で数kΩが必要だったのだろう。基板に並置する Mos FET は、触って熱いわけではない(60°程度か)が、0.3mm厚銅板へ の半田付けを試した。出力回路のP-chとN-ch素子は、共通ドレインを出力するから、共通の放熱板を直付けできる。半田付けを手早くすれば熱破壊の 恐れはない。音質は、負帰還型 1 bit アンプの明快な音質、微妙な違いは、抵抗分割が10k+1kは、22k+2kと比べてかっちりした音で余裕なり甘さがない。 Trの反転を利用して貫通を防いだ出力回路は、その複雑さが欠点である。同程度のできは Trでは容易だったという思いがある。

負帰還は負荷の両端電圧を各IN入力へ戻して、負荷の両端電圧が入力VRの両端電圧を再現するなら話は単純である。もし、コンパレータの出力TrがCE 分割でなく、エミッタ接地にしてそれをCEFで受ければ、各コンパレータは入力のVRの両端電圧を再現すればよく、両コンパレータと両出力回路は独立 に動ける。それは、単純で容易な回路であり、正しいのはそれしかないかもしれないが、そうでなくCE分割では負荷の片端だけの電圧再現も独立でない。 ひとつの電圧の再現にふたつのコンパレータが関係している。他方のコンパレータがOFFなら、コンパレータは自由にON/OFFして入力に負帰還電圧を 追従できる。他方のコンパレータがONのときONにならない排他制御には LM311 のストローブ入力を利用できそうだ。

ストローブ入力pin 6は、コンパレータ初段の差動増幅回路の +Vcc からの負荷抵抗の一部、電源から-1.5V程度を下に引き出力TrOFFにする。 ストローブOFFの開始終了遅延をデータシートは載せていないが、IC内部への制御だから決して遅くないだろう。pin6,5 を結合して下に引けば初段差動 のバランスを崩すことなくストローブOFFでき、pin6 だけを動かすよりも影響を引かないように思う。両方を下に引くのは、(1.3k+300)/2=800Ωの抵抗 をVccとの間に持つことであるから、CE 分割の下側も 800Ωにする。これは最大の電源電圧 +-18V で 22.5mAでありまだ可能である。コンパレータの pin5,6からの電流を他方のコンパレータ出力Trのコレクタ pin 7 に入れるとその出力Trの負荷抵抗にもなる。余分なTrなし、CE分割のコレクタ側の 外部抵抗なしにストローブ制御できそうだ(図18右)。

なお、図18左は、CE分割のGND側でON電流をTrによって他方のpin6に与える案。pin6 のSTROBEは3mA程度引けばよいが、-Vccからでも同じだろう。 図18中は、CE分割の上にTrを互い違いに使って双安定FFにする案だが、まだうまくいくとは思えない。

入力電位が正のとき他方をOFFにして一方のコンパレータだけON/OFFし、入力電位が負のときには、そのコンパレータはOFFで他方のコンパレータだけ ON/OFFするという手もある。しかし、入力の極性によって動作を切り分けるのはクロスオーバー歪みの危険があるため、入力のオフセットは利用せず、 他方ONならOFFにする排他論理だけを使う。CE分割のE側の電位が高くなれば下側のMos FETがONになり、ドレイン電位は下がる。これは、コンパレータ 出力TrのE接地と同じく-INへの帰還が負帰還になる。大きな入力容量の Mos FETのためには、Tr による電流供給回路も考えられる(図20)。

ステレオでは各信号の中点をGNDにすると左右で独立のGNDになり、各GNDは電源のGNDとC結合できない。負帰還CRのGNDを入力信号の中点に結合する。 出力は、そのGNDに対して10倍程度増幅される。そのため出力は対称ではなく1/10程度ずれた対称である。左右は、各負帰還CRの中点を入力信号の中点 にして、入力の中点をつくり出す抵抗はふたつのCRのR直列で代用でき、CRのC直列の中点と2抵抗中点を結ぶ必要はない。入力の低抵抗をさける2kはVR の前に移動して、図19は、図21になる。これは結局、CRの並列を+IN/-IN間にもつ回路である。入力信号の反転なしに両コンパレータを同一電位差の 逆動作にする。出力の負荷両端からの負帰還を-IN,+INにいれ、他方のコンパレータは+IN/-IN入換えである。入力はVR出力の両端を抵抗を介して +IN/-INにいれる。負帰還と入力は加算し同列に扱われ、負帰還される出力だけでなく入力信号にもLPFが掛かるが、可聴域外だから問題ないだろう。

そうして作成した回路は、またしても危険な発熱回路だった。LM311のSTROBEは働いてくれていないようだし、テスターで出力電圧をみると、片チャネル は、これも問題だが0Vで安定しているようで大して発熱しないが、片チャネルは正常に電源電圧の1/2が出ていたのに触れないほど熱いのを何回かするう ちに動作が変わってしまい、それより明らかに低い電圧になった。熱による素子劣化と思う。いくら考えて正しいと思っても実際の動作が保証されるわ けではない。試作は必要であるが、その作業が変わらないのに、成功と失敗の落差は大きい。こういうとき、すぐ別の方法を考え、この方法がなぜ失敗 するかの認識を避ける。BTLはTrのCEFでやるのが安全な方法だ、これまでシングルブリッジもTrはMos FETよりずっと容易だった、シングルでも十分な 音量でありBTLに利点はない、そのような考えがいくらでも出てくる。

左右両チャネルで同時にテストする必要はない。電源線を独立にしてまず片方で成功する必要がある。LM311 のSTROBEは、電位で電源電位から何V下げ るとOFFになるのか。動作が高速でないのか。という疑問が出る。STROBEはいままで、(1)pin5,6 とも浮かせる (2)pin5,6 を結合して浮かせる、(3)両 方を電源に結合する、と変化させた。全てはシングルブリッジが安定的に動作するために経た道だった。それを放棄して (4)pin6 だけを下に引く、 (5)pin5,6 を結合し下に引くを試した。(4)(5)でSTROBEは正常に動作していないように見える。((4)は実はpin5 だけを下に引いていた。)

VRは回路の電源とGNDから浮かせて、コンパレータ入力の+IN/-INへVRは直結した、それがだめかもしれないと、その後、VRを外して入力なしで動作させた。 これでは負帰還も差動に出てこれないのかもしれない。片側の例えば-INへの負帰還はその逆側のインピーダンスが低くないと差動に反映しない。 のれんに腕押しになる。

昔の特別演習のB5の青刷り資料が出てきたので引用する。

システム基ソ論Bの田村さんの話の中の、ディザーによる線形化の原理である。ディザー波形の逆関数のシステムとなってしまうので、三角波または ノコギリ波を使うと線形になる。

・試作したアンプは、2SC306を出力に使ってTTLの回路をまねたものではある程度成功したが、大出力を出そうとためしている途中で回路上の色々な

問題がうかび上がってきた。現在の回路は、2SC1014ー2SA624コンプリメンタリー出力ブートストラップ回路でパルスアンプ部分はうまくいった。

・ノコギリ波発生、ブートストラップ回路の問題点。

・電源では非常に苦労したこと。

(以上引用)

阪大基礎工学部生物工学科の3年生の特別演習は、テーマを全く限定しない自由研究で単位をひとつくれた。8人6組がこれに応じて自由研究を行った青刷り レポートである。私以外のタイトルは(敬称略)、池田頼信、入江真行、大敏明の "プラナリアの条件反射について"、牧川方昭の"神経系の進化"、中村清 の""大阪府自然環境保全条例"の本質についての若干の考察"、山下良藏の"AD変換の実験"、駒田洋の"真空管アンプの製作"があった。 その駒田洋氏の記述から昭和48年(1973年)7月末とわかる。

図23(a)で初めて動作し、発表の頃に(b)になった。昔も今も私は変らない。タイトルにあるように (未完成)である。当時も"大出力を出そうとためしている 途中で回路上の色々な問題がうかび上がってきた"、今もそうである。(a)では上下の素子にNPNを使用し、上素子のベースにダイオードによる電圧降下を使 い下素子ON時に上OFFを確実にする。前のTrのON時にエミッタ側の100Ωによって下がONであるとき下のVceは小さいがVbeは0.7V程度ある。そのとき上のVbe =前Vce+下Vbe-下Vceであり、下Vbe〜0.7Vで、前Vce=下Vceなら、上Vbeも0.7V程度であり、OFFが確実でない。ベースへのダイオード直列は、上OFFを確実に するが、前TrがOFF下OFFのとき、電源から0.7V無駄にする。上素子は電源電圧-R*Ib-Vbe-0.7Vを出力するエミッタフォロアである。

(b)は、コンプリメンタリ・エミッタ・フォロア(CEF)にブートストラップを使用している。CEFの出力からドライブ回路のコレクタ抵抗の上に返すコンデン サとダイオードのブートストラップ回路は、共通ベース電位を電源以上に上げる。これなしではOFF時の出力電圧が電源電圧から低下したところまでしか上 がらない。CEFのNPNはエミッタ電位を上げるにはベース電流を流すが、これが700Ωの電圧降下を受け上昇を妨げる。そのため、上昇は緩やかでVcc-0.7Vの かなり手前で停止する。ブートストラップのコンデンサは出力変動を通しダイオードがVcc以上にする。700Ωの抵抗上端には下端の電圧変動がCEFで低イン ピーダンス化され再現して、現実よりも大きな負荷として働き電圧ゲインが稼げる。しかし、出力変動が乗る抵抗上端にVccの2倍の電位は発生しないし、 抵抗の両端間電位は、コレクタ電流がON/OFFするから変動しないはずもない。電源以上の電圧を供給する回路は、Mos FETのCSFの数V確保に、GND以下を得る のにも使えるかもしれない。アナログSEPP出力回路でのブートストラップは、当時、市販品アンプにも使われ、後に準コンSEPPの音の元凶といわれる。 こんな不可解なものに頼る回路は不安定で発振しかけたような奇妙な音になるのだろうが、1 bitアンプではどうだろう。当時のPWMパルス回路では横に揺れ る縦線以外に波形の肩の部分に波打つ部分が上下に揺れていたのはブートストラップが原因の症状だろうか。

1000pF//5kからクランプダイオードを結合した+IN/-INまでの間に10kを直列すると、ノイズは全くなくなるが電源電流が片側LM311動作で0.3A,0.7Aとなり (入力コンデンサに5nFを並列しても同じ)戻す。抵抗なしではダイオードの働く0.数Vの電圧まで1000pFのコンデンサに電圧がたまらず動作できず、大抵抗 の直列ではコンパレータゲインを下げるのと同じなのだろう。適切な抵抗値を探して抵抗を下げていき、白色雑音が出没する100Ωに替える。そのとき電源 電流はやはり大きい。VR最低では白色雑音ありで0.2A、止まると0.08Aだが、VRを上げると最大0.7Aまで増大。電源SWの電流値を見て止めコーンが飛び出す のを見てDCと知る、放熱板なしの素子温度が上がる前に止める各回1秒程度の電気入れである。電流は定格以内だが熱が問題で素子は150°以上は特性劣化 の危険がある。少量の電源電流で動作しシングルブリッジの音質と違わずその4倍の音量が出るBTL動作を期した回路変更を繰り返している。

中点からの-IN への結合を外した電流は小さく(0.05)、VRを上げても0.2A程度。しかし、出力電位はVcc/2より低く、音量も小さい。相手のLM311がOFF時 の浮動が問題かと中点から両出力に各1kを繋ぐが影響なし。相手側のP-ch Gate に繋げたSTROBEを外すと1.75Aも流れる。この形での動作は無理かと思う。 まずは、安全なTrのコンプリメンタリ・エミッタ・フォロア(CEF) で入力の両端電位を再現するBTLを動かすべきかもしれない。CEFは貫通の心配がない CEFは基本的に電圧を出力する回路であり、BTLは負荷の両端に入力の両端電圧の何倍かを再現する。それでも両者が違う電位を出力するとDCが出るが、 コンデンサを並列した電源GNDの中点電位を使うシングル・ブリッジ回路ではDCが出ないからさらに安全だった。両端がHHとLLの場合、負荷には0を出力 するのと同じで両端電圧の差だけが負荷に与えられる。そのとき両端の電圧を作り出すふたつの回路は独立に作動でき、それぞれがシングル・ブリッジ と同様にON/OFF動作して電圧を再現すればよい。

それに対して、負荷に電流を供給する回路は、その逆向き回路と同時作動できない。同時にON作動するだけで電源からGNDへ電流が貫通するからである。 これは電圧を出力する回路が両端に同じ電圧を出して問題ないのと比べて、難しくて当然である。それぞれが負荷に流す正負の電流を作るコンパレータ は、独立作動できない。両方OFFはよいが一方がONするには他方がOFFであるべきをLM311のSTROBE機能を使った相互排他で実現しようとした。しかし、 これはひとつのレベルの領域分割である。正区間に一方がON他方がOFF、負にはその逆をあてるとき、0の近辺でON区間が重なる危険を避けるため、間に 設ける両方OFFの安全地帯は、同一のレベルを入力したふたつのコンパレータのオフセットで調整されるから、ある程度の大きさが必要である。一方、 線型性のためにはそれはできるだけ小さくなければならない。そういう相反する要求である。つまりこれは、動作原理的に2値でなく +1,0,-1 の3値 制御によるアナログ値再現である。系の入出力の非線型特性は負帰還によって改善されても、間のOFF区間は、0近辺の小さいデッドゾーンとして消えず 残り、ダイナミックレンジに影響する。最大音量は、電源電圧とスピーカーコーンの可動範囲から制限される一方、最小音量はアンプの静寂さで、雑音 と線型性で決まり、どこまでも小さくなければならない。実際は微小信号は、雑音によってマスクされ、非線型特性のデッドゾーン、ヒステリシスによ って消える。1Vの信号にとってこの安全地帯は60dBで1mV、80dBで0.1mVでありコンパレータのオフセット電圧数mVでは60dBの線型性もないことになる。

結局、コンパレータによる反転/非反転BTL回路が正常に動作した。非反転と反転増幅を使えばアナログ信号の反転や入力信号の両端を扱う必要がない。 非反転D級増幅回路は、いままで紹介してきた実績ある回路で、もしそれしか動作できないなら、入力信号の両端電位を増幅して負荷の両端に拡大再現 するしかないが、それはステレオではうまくない。なぜなら、入力LR信号の接地側が共通なのでLR信号のそれぞれの中点は一致できないからである。 電源を共通にする左右の回路が基準電位を別々に動作することは容易ではない。基準電位はGNDにコンデンサで落したいので左右で共通にしたい。 基準電位を例えばLRの信号端から各1/4、逆端から1/2の重みで平均した電位にすると、LRが同相ならBTLと同じ出力が得られるが、片方しか信号がない LR独立、または逆相信号の状態ではBTLにした効果がない。統計的にステレオは同相がほとんどで逆相は小さいから、ほとんどBTLの効果が得られると 納得できるだろうか。そのとき "もしかすると、コンパレータによる反転型増幅が可能かもしれない。" という考えこれが多くの失敗アイデアに紛れ ていた。

Trによる反転はだめでもコンパレータによる反転増幅は可能だった。非反転回路は、コンパレータの+INに(直列抵抗5kつきで)信号をいれ、-IN には 10k+1kの抵抗分割(直列抵抗による電圧分割)とコンデンサ5nFの1次遅れLPFのNFBであり、それに対して、もうひとつのコンパレータを使う反転回路は -IN側の51k+5k抵抗分割NFBの5kの下側に入力を繋ぐ。非反転のコンデンサ5nFと1kの下側と反転の+INは、1k+1k+0.1μの中点電位に接地する。反転型 も非反転型と同じくコンパレータの+IN(pin2),-IN(pin3)間に1000pF(102)のコンデンサと高速小信号用ダイオードを逆向き並列しクランプダイオード にする。反転回路ではこの1000pFと5Kの時定数でLPFが動作する。

いつものようにコンパレータ LM311 は、速度を確保するため、pin5,6をVcc(pin8)へ結合して初段の電流を増やす。高速化のため1kから減らした750Ω 負荷はpin7出力をVccにつり上げるエミッタ接地型のコンパレータ出力である。コンパレータ用の電源GND線とCEFの電源GND線は別にして、750Ωの上は CEFのVccにpin1はCEFのGNDにつなぐ。各コンパレータ、CEF近傍の電源GND間に0.1μFの積層セラコンを付ける。CEFは、2SA1359/2SC3422のペアを使う。 耐圧40V、電流は3A、もう少し大電力のTrに差し替えも考えられるが、そうするとCB間容量が大きく、価格はこのペアの2倍以上になる。ステレオのBTL 回路は、CEFを4つ、出力Tr8個使う。ここでの100円の差は部品代で800円の差になる。安価でないと誰も使わないから、先ずはこのペアで動かそう。

18V0.8Aの電源での電流は、無音時0.19A, オルガン音楽による最大0.6A。無音時電力は18x0.19=3.4W。コンパレータの電源電流5mA、負荷電流が18V/0 .75=24mA の1/2の和17mAの4倍68mA、中点電位の2kを通した電流9mAを加えて77mA (190mAの40%) は計算にのるが、残り不明。

その後、箱の天井高ぎりぎりの放熱板が基板上0.1μの積層セラコンによる傾きで箱に入らないので、0.1μを基板裏に移動し、薄アルミ板クリップ止 めによる放熱板テスト中に音が悪化し、出力の片chが歪む。放熱板による出力ショートか、配線ミスによる片BTL固定が原因か。 CEFのBTLは、電圧型 なので出力逆側端子をケミコン接地のシングル動作で不良箇所の特定ができる。ステレオの片側のchのBTLの音と、BTL相手側のシングルの音は正常。 ひとつのCEFだけ音がVRが小さいときは音がなく、VRを上げると音がばりばり途切れ閾値を伴う非線型の音である。CEFを解体して行なったテスターに よるTrのダイオードテストは意外に正常であった。抵抗計によってCE間の電流を測りCBの間に指で触る増幅も確認。CEFのTr交換後に(1)PNPのエミッタ の半田付けが外れたとき、歪みか異常発振か区別できない音が出る現象と、(2)NFBが外れたとき大きな閾値を感じさせる音が出る現象を知った。(2)が 交換前の現象であったから、CEFのTrを疑い交換したが、単にNFBの接続不良、という余分な交換だった。

単一電源型1台目を追出し箱にいれ、リビングで長く大音量を出すとアルミ製箱が結構熱く(40度〜50度に)なった。密閉箱では問題ありの発熱である。 これに比べるとシングルの発熱は問題にならない。放熱板なしで問題なく箱が温かくなることもない。小さい部屋では十分な音量であり、BTLは大きい 部屋で鳴らすためだけである。しかし、電源の能力を生かすにはBTLは避けて通れない。

シングル動作で、ブートストラップ回路をテストした。Vccと750Ω上端との間にダイオードを入れ、CEFの出力エミッタから5nFで750Ω上端に結合。 音の差は明確でない。波形が十分上に伸びなくても平均出力である音はNFBによって差が無くてよいが、発熱差も明確でないので採用しない。

正負2電源型アンプに修正。(1)最大VR時の小さな白色雑音(低インピーダンス時のクランプダイオードノイズ)を直列抵抗で消すため、VRから+INまで のシールド線をやめ、間に直列に5kΩをいれ線長の大半をVR側にして、拾った帰還を5kΩと+IN/-IN間の1000pFのLPFで除去する。(2)出力端子をワン タッチターミナルに変更。(3)ポリスイッチ RXEF090 は保持電流が大き過ぎ取り去る。 (4)この正負2電源型アンプの音質の他のアンプとの音質の差 は高域の甘さである。22k+2kと5nFでは時定数が10μS、高域カットオフ周波数が16kHzでは低い。10k+1kに変更。

単一電源型の1台目にも、(1) VR最大付近でノイズが発生し入力の20kVRから+INまでの間に5kΩを入れた。NFBの抵抗分割は22k+2kのままにした。但し、 2台目の単一電源型は、10kVRと+IN間に抵抗なし(3)で正常であり、入力直列抵抗の必要性には不明点が残る。この単一電源型1台 目から中点電位のケミコン(2200μF16v)を取り去り、反転型コンパレータ回路(51k+5.1k+1000pF)と4CEFにアルミ(2mmx15mmx50mmx4(1mをハンズで買っ て切る))放熱板を増設し、2台目のBTLにした。反転CEFの発熱が非反転のそれより明らかに大きい。触った感じで非反転が60度なら反転は75度である。 1台目BTLも発熱で鉄放熱板が熱かったが非反転も同程度だった。非反転が22k+2kと10k+1kの違いか。周波数測定では反転と非反転で違わず2MHz〜2.4 MHz程度である。 (122kB 8/20 2009)

回路のアイデアは動作させて初めてそれが正しいかどうか確認できる。それを毎回ユニバーサル基板でテストしていては、ほとんど、そ れぞれの回路毎にボードと部品が無駄になる。基板の再利用は、全体に対する解体部分の比率が少ない場合にだけ意味があり、解体に手 間がかかるなら、新しく配置を決め新しい部品で回路を組むほうがよい。それほど回路の解体は時間を要する作業である。ユニバーサル 基板ボードも前述のように私は安いもの(秋月¥650の1/4)を使ったが、通常ガラスエポキシのユニバーサル基板の両面スルーホールメッ キ付きの価格は決して安くない。私は半田付け作業に入るのが常に早過ぎた。古いベークライト小基板1枚を入れると、1bitアンプ回路 ですでに計7枚のボードを製作していた。

試したのは、コンパレータとTr CEF を介在した Mos FET CSF である。負帰還 1 bitアンプのような高周波パルス回路は、やはり配置が 重要であって、配置変更をすれば音が変わる。写真のように入出力する部品を用意していればブレッドボード上の作業は少ない。 次の(1)〜(3)が分かる。

(1)Mos FET のコンプリメンタリ・ソース接地は、Tr CEF でドライブすれば安全かと試したが、18V 0.8A の電源からいきなり 1.7A流れ る。そこでCSFに変更。Mos FET のCSFにはコンパレータ出力との間に Tr CEF のドライバをいれるのが有効と判明。それを入れたり外し たりして音質の違いを確認する。それがないと音が歪みやすいのがピアノの音でよく分かる。1 bit アンプのこのような音の歪みは正常 な発振とは違うモードでの異常発振によるものであり、回路の配置に依存する。Mos FET の入力容量をドライブするには能動素子Trによ るほうが抵抗によるよりも容易である。Tr ドライバによる効果はその遅延の影響より大きかった。TrのCEFではもう少しコンパレータの 負荷抵抗も大きくして消費電流を下げられるだろう。

(2)コンパレータ入力のクランプダイオードはなくても正常に動作できた。そしてコンパレータのバランス入力 pin5,6 は両者を互いに 連結する必要があるだけで Vcc に結合しなくてもほぼ正常動作できた。このような知識は、半田付け作業では得られない。半田付けで は、一度、問題をある方法で解決したら、ずっとそれを使い続ける傾向がある。それを外してみるのにも作業を伴うからである。それら はその状況で効果があっただけで、別の状況では必要でないかもしれない。このようなテスト基板を使えば、それを試すことができる。

(3)中点電位に負荷の逆端を繋ぐのは、DCがNFBループの外になるから、ケミコンを使っていながらDCまで出る回路であるが、出力電位の 制御ができず、それの平均が Vcc/2 にならない。Vcc= 18.3V で出力電位が 7V 程度である。この現象は、どういう原因だろうか、と考 える。負荷のスピーカーの逆側に繋いだケミコンの上端を中点電位から外すと、DCが回路のNFBループに入り、Vcc/2 の中点電位が崩れな くなる。しかし、電源ON/OFFの音が巨大になり、DCアンプでなくなる。ACアンプの音には限界があり、ケミコンの特性が出るのか独特の 歪み感がある。出力の逆端を中点電位に繋ぐだけでそれらの欠点が消える。

しかし、その方がよいかとやってみると、その近辺が拾ったハムを含めた雑音が音楽に乗ってくる。出力電位が中点電位に制御されると、 それまで負荷に音楽ソース信号しか出なかったのに、中点電位にのる雑音も負荷に出てくる。さらに電源ON/OFF音も以前と全く違って巨大 である。出力の同相電位を制御するのと出力を制御するのは裏腹のようである。やはり、負荷に出る音が最も重要であり、出力電位が多少 偏移しても、それを安易に負帰還すべきではないかもしれない。なぜなら、負帰還というのは入力信号への加算を伴うからである。

しかし、中点電位がVcc/2から大きく外れると出力振幅が制限されるから、弱い制御が必要と思われる。+INの中点Cから-INの5kの下側Aと の間を直結でなく低抵抗で結合すれば、1k+1kの中点は並列インピーダンスが500Ωだからと1kΩ,100Ω,50Ω,10Ω,4.7Ωを試した。 -INに入る電圧と+INに入る電位はその差がA,C間の低抵抗(例えば50Ω)で作られその場合、約1/10が負帰還されるためオフセット電位は、 その逆数10倍に拡大される。50Ω以上で9.1Vであるはずの出力電位は9V近辺である。10Ωでは50倍で8.8Vになる。4.7Ωで8.5Vになる。 これぐらい(0.6V)の偏移はまだ問題ない。LM311のオフセット電位は2mV(typ)7.5mV(max)であるから、その100倍で200mV、最大750mVであ る。電源ON/OFF音はなんとしても避けたいものだが出力電圧の偏移を避けるために低抵抗が必要であり、直結の0Ωではオフセットが無限 大倍(実際は1000倍程度)される偏移が問題であり、動作の不安定性の原因になる。この低抵抗が開放では18V程度の電源でもFE83のコーン 紙の移動は電源ON時に1cm近く飛び出し、OFF時には逆に引っ込む。この低抵抗を直結にすればON/OFFでコーンは全く動かないが、50Ωで 数mm、4.7Ωで1mm程度動く。ON/OFF音も4.7Ωではわずかである。

この問題が、オフセット電圧の拡大と分かっても、それならオフセット電圧の調整の半固定抵抗をコンパレータ毎に使えば低抵抗は不要 ともいえるが、却って繁雑である。空間から拾うハム雑音は基板を箱に入れれば減少するが、雑音を避けるにはできるだけ低抵抗がよい。 シングルブリッジでのこの不思議な回路(負荷の逆側を中点電位に繋ぐ)によるDCアンプ化は、音の透明さと普通にある雑音への非常な耐 性をもつ回路だから是非試すべき回路と勧めたい。つまり、差動入力に入力信号しか入れなければこれほども回路が雑音に強くなるか、 という見本のような回路である。

なお、出力電位の偏移は、BTLでは有害なDC誤差になるからと心配するかもしれないが、この低抵抗は、BTLでは使う必要がない。BTL回路 では負荷の両端を独立に共通の中点電位を基準にして正負の信号を加算するだけで、負荷の逆端を帰還していないため出力電位の偏移も 小さい。そして実際、BTL1台目の回路でそのような出力電圧の偏移もないし、電源ON/OFFの音も全く無い。なぜなら、BTL回路は、もとも とDCアンプである。負荷の逆端のコンデンサの電位を帰還するのはシングル特有の話で、BTLではその必要がない。シングルでは出力電位 の少さい偏移は有害でなくこの低抵抗は5Ω程度がよい。これを避けて直結の0Ωのままでは、電源電圧は18Vであるのに、約11%もずれた 中点電位7Vのアンプは、7Vの2倍の14Vの電源の音量(60%の電力)になる。

ブレッドボードでMos FET CSFシングルが動作し、その反転回路版を併設し、1 ch の BTLをテストした後に、前に Mos FET CSG で苦しんだ ユニバーサル基板を思い切って改造し、Tr の CEF でドライブする Mos FET の CSFの BTL 回路(ステレオ)が動作した。CSG は CSF より明 らかに難しかったからである。ブレッドボード片 ch回路で、コンパレータ LF311 の負荷は 1k, 2k, 3kと変えてテストし、3kでは音質にノ イズが混じったので 2k にした。そのとき電源電流は、それぞれ 76mA, 64mA, 59mA であったが、ステレオBTL回路で無音時の消費電力は、 18.3V x 0.087= 1.59W である。Tr の CEF のステレオ BTL 3.4Wの約半分である。通常の音量で 100mA 以下であり、Tr CEF の BTL回路と比 べ電力効率がはるかに良い。もちろん、18V電源で8Ω負荷で最大出力 20W で 1.1A程度までの電源電流が流れる。それが供給できなければ 出力が制限される、その大出力時の効率を調べたわけではないが、大音量時の8個の Mos FET の発熱は小さく放熱板なしでもいけるようだ。 つまり、Tr の CEF にあった発熱の問題は、Mos FETの CSFでほとんど解決したと思われる。

今回の回路では、コンパレータの LM311 の pin5, 6は、結合だけでVccへ結合せず、負荷抵抗2kへ流す電流と pin1 も配線が局所的単純さを 優先し、コンパレータの電源とGNDに結合した。コンパレータの+INへは直列抵抗なしの直結とし、-IN 側へは 5.1k+ 51k の負帰還、+IN/-IN 間は、クランプダイオードを省略し、コンデンサ1000pF だけにした。コンパレータと Tr の CEF、そして Mos FET の CSF のステレオで4つ の回路は、同一にした。入力と中点電位を+INと5.1kの下側とのどちらに結合するかだけで、非反転回路になるか反転回路になるかが決まる。

負帰還の抵抗比 5.1k:51k= 1:10 は 1:r とすると反転回路ゲインは -r、非反転回路のゲインは r+1 である。r=10 では反転-10、非反転 11 で絶対値が1違う。入力1に非反転が11、反転が-10を出して差の21の電圧を負荷にかけるのがBTLであるが、両方のアンプのゲインが違うとク リップが始まるとき他方はまだ最大に達しないため出力振幅が十分使えない。同様な問題は、電源とGNDの中点電位がずれても起きる(前項参 照)。11:10は許容範囲とし、ゲインを合わせる抵抗比調整はしない。反転/非反転の回路共通化の利点のほうが大きいからである。 周波数は、無音時に 2MHzの近辺下で、音のあるときは2-2.5MHzであり、問題はない。安定で発熱も少なく、現在、最良の回路である。

ブレッドボードは、回路だけでなく素子特性を見るのに使える。シングルブリッジでの CEF のTr取換えをテストをした。BTLでない回路 でステレオでなく片チャネルの音質の評価は耳に厳しい。ステレオ再生は音場再現の美しさに惑わされ音質評価が甘くなる。さらにBTL は音量がどこまでも出ることに酔う。小ブレッドボード上では回路規模2倍のBTLはできても、さすがに4倍になるBTLのステレオはできな い。が、まずはシングルで正常でなければいけない。

コンパレータは1k負荷エミッタ接地である。2SA950/2SC2120ペア、2SA1015/2SC1815ペアでも鳴る。大電流が流れないトランジスタでは 音量がでないだけで基本的に同じ音が出るべきが音質に差がある。それだけでなく、多く使ってきた 2SA1359/2SC3422 (40V3Aまで使え る低速スイッチング用)は、ブレッドボードテストで結果がよくなく、1段CEFでは音が濁る。今までユニバーサル基板ではこれをすっき りさせるために色々対策をしたが、もともと原因は若干ドライブ不足だったのかもしれない。

Mos FET 2SJ377/2SK2231のCSFも直結では音が濁り、Tr のCEFでドライブすればOKである。Mos FET の容量性入力のためもあるだろうが、 症状は同様なドライブ能力不足にみえる。もちろん、2SA1015/2SC1815 CEFは音がすっきりしているが低音が少ない。2SA950/2SC2120ペア ではもう少し音量がでる。両者は、直接コンパレータ直結で問題ない音がでるが、大電力用のTrは、ドライブTr CEF が必要である。 古い 2SA636/2SC1098 はさほどでないが50V5Aまで扱える2SA1931/2SC4881も 50V10Aまで扱える2SA1887/2SC5000も Tr CEFでドライブしな ければ音が歪み無音が濁る。

音質の差は、アナログアンプのトランジスタの音質差がそのまま1 bitアンプに出るわけではない。ここで紹介する1 bitアンプは、大き な負帰還で動作している。この負帰還を外して動作させることができないし、回路と素子の裸の線型特性は全体の特性には関係しないは ずである。音質差が出る要因はアナログ回路のように多くなく、スイッチング特性(レベルの飽和特性、スイッチング速度) の優れたTrが よい音質を出すだけと考えられる。コンパレータという非線型増幅素子を電力増幅しただけの回路にLPFフィルタ付きのNFBを掛けるだけ だからである。

これがドライブ能力不足のためでなくバランス端子 pin5,6 をVccから外したこと、クランプダイオード除去、負荷1kによるものなら、 それらを戻せば解決するかもしれないと思って、pin5,6をVccに繋ぎ、クランプダイオードを付け、2SA1359/2SC3422で試してみた。 これはかなり回復した。それでも MosFET の 2SJ377/2SK2231のCSFでは負荷を510Ωにしても音は改善されない。やはり、Mos FET CSF には Tr CEF ドライブが必要なようだ。

それに対し、CSGは、上側は P-ch FETで電源電圧のソースからゲート電位を下に引くだけでドレインの出力電位を電源に接続し、下側の N-ch はGNDをソースにしてゲート電位を数V上に上げるだけでドレインである出力をGNDにONする。ゲートの参照電位は固定のソース電位 であり、ゲートに与える制御入力は、出力(ドレイン) の影響を受けない。これこそスイッチとしての基本機能である。これが動作すれば、 出力の負荷の電位は、電源とGNDのいずれかに接触することで出力のパルスを形成する。すなわち、CSFは電源とGNDの任意の中間の電位を 扱う回路であって、両端の電位を扱うのが苦手であったのに対して、CSGは電源とGNDしか扱えない。しかし、それは欠点ではなく 1 bit アンプに唯一必要な機能であり、CSGが最終的に1bitアンプの機能を満たす回路であるが、いままでこのCSGが成功しなかった、それはな ぜだろう。

それが難しかったのは、CSGを負荷に電流を流す電流源と扱ったからで、H型の斜め2個の素子をON/OFF動作させると考えたからではないか。 そこでは中間に安全地帯をおく、3値によるアナログ電位の再現という構図になる( 5.7 参照)。それを、H型の片側 の上下素子で負荷の1端の電位を再現させると考えればCSFと同様にH型の上下素子をひとつのコンパレータ制御にすることになる。 その上下素子の間に貫通があり得るが、貫通を避けるにはレベルで避ければよい。それは以前に Tr による反転ドライブで可能だったし、 それ以外の回路もあるに違いない。

以前のTrによる反転回路は、コンパレータ出力(コレクタ)をエミッタ接地の2回路(上PNP、下NPN)で受け、各反転してMos FET の CSGの ゲート電位(上P-ch、下N-ch)に与えたが、一見上下対称なこの回路はじつは非対称である。上下対称ではコンパレータ出力が中央(Vcc/2) で上下TrON、後続の上下FETがOFFであり、コンパレータの出力TrON時はGND近くを出すから下側 Tr OFF(FET ON)は問題なくできるが、 コンパレータTrOFFでは対称回路ではFETは上下ともOFFであり、コンパレータOFF時に出力がかなり上でないと上側Tr OFF(FET ON)にでき ない。そこで下側のドライバTrのベース抵抗値を上側より高くして上下非対称にしている。そのため下側のTrのドライブ能力が制限され るだろう。

コンパレータ出力がエミッタ接地でTrが上下とも反転がCSGのひとつのドライブ方法であるが、コンパレータ出力のTrをCE分割とすると、 上下ドライバ素子の一方がエミッタ・フォロア(EF)で、もう一方が反転なら、後続のMos FET は電源GNDをソースにしてドレインを結合 した出力にするCSGにできる。例えば上下ともNPNで上がEF、下が反転でもよいが、Trドライバを上下ともPNPで上が反転(EG)下がEFなら、 コンパレータ自体と符号が変わらず -INに負帰還できる。NPNを使うと符号が逆転する。

この非反転型シングル回路をブレッドボードで動作させようとして、しばらく悪戦した。ひとつは発熱が収まらないことだった。CSGは、 発熱をさせないためにとる回路なのに貫通電流がある。CSGひとつで電源電流が0.2A近く流れる。もうひとつは音が正常でないこと。 途中で下側のエミッタフォロア動作電位を下げようとしてダイオードをもうひとつベース側にいれる回路テストで2SK2231を1個熱破壊した。 電流を落とすものなしにダイオードをTrベース側に向け、この下側FETはONのままになり上側がON時に貫通電流が流れたのである。 どうしても雑音が消えなかったのは、+IN/-IN 間の1000pFのコンデンサだけに頼ったからだった。前に成功した上下Trでの反転回路に戻し ても同じ音質の症状が出て、ブレッドボードでは無理な回路かと一瞬思ったが、以前は非反転シングルの回路が+IN/-IN 間の1000pFの セラコンだけでなかったことに気が付き、抵抗分割 51k+5.1kの時定数が限界近くだったからか5.1kに5nFを並列するとピタッと雑音が 消え音が澄んだ。ブレッドボードでもこの程度の回路が動作できるとこれで初めて分かった。

発熱の問題は上下Trとも反転の回路( 図16(d) ) から下のEF Trを取り去り、CE分割のE(pin1)に抵抗270Ωをいれ、 直接下側のN-ch FETをドライブする。このエミッタの抵抗値と上側の反転Trの動作を決める2つのベース抵抗値によって、コンパレータ コレクタ電流において、上の P-ch FETのONからOFFに変わる閾値電流Θ1よりも下のN-ch FETがOFFからONに変わる閾値電流Θ2を大きく (Θ1<Θ2)して、Θ1以下で上がON、Θ2以上で下がON、と両方のON領域を分離して貫通を避ける。つまりこれは、同時にひとつしか取ら ないとする電流レベル分離による貫通回避である。コンパレータの電流が即時に出力のFET状態になるわけではないが、その間の遅延が 両閾値間の遷移時間より小さいなら、これによって貫通を避けられる。シングルアンプが電源電流50〜60mAで正常に鳴る必要がある。

さらに電源SWに電流計の10A端子をあて導通時の電流を測定しては音を聞いて確認を繰り返す。音に影響しない範囲で電源電流値が小さ くなるよう抵抗値を探す。CE分割のエミッタ電位は、ON時3V程度でよいからコレクタ側の抵抗を2kにしてON時の電流を10mA程度にする。 コレクタ側の抵抗は、電源に2k+510で抵抗分割されて上側の PNP Trのベース電流になり、このTrのコレクタ電位を P-ch FETのゲートに いれる。ONに必要なゲート電位は電源-数Vであり、Tr OFF時に4Vもあれば十分だから、電源電圧を分割して1/3.5にしてインピーダンスを 下げる。電流が少なくシングルが正常に動作した回路と抵抗値を図29に示す。Tr CEF + FET CSFと比べTrが減るが残念ながら抵抗が4本増 えた。Mos FET CSGの発熱は少なく、小音量時47mA〜50mAであり放熱板なしのFETの金属のドレインに触って熱を感じない程度である。 おそらく30°程度であろう。

容量性負荷には出力にLを直列して防ぐ。D級アンプのフィルタ用に売られる22μHのインダクタンスを負荷に0個〜4個直列して60mA,48mA, 42mA,37mA,33mAとなった。22mAを引くと38mA,26mA,20mA,15mA,11mA。確かに無駄電流が減るが下がり方は少ない。インダクタンスのイン ピーダンスは、2πfL 6.28*22=138から、1MHzで138Ωになるはずがfが1桁小さい。周波数カウンタで調べると132.7kHzで2πfL=18.3Ωで ある。それなら理解できる。高周波の不要輻射フィルタは、定量的把握ができず未着手だった。このように電源電流の数値に反映するな ら把握ができ、無駄電流を減らす意味も明確である。小型のL(22μH)を各chに1個使い、効果を出すには基本周波数が高い必要がある。 5.1kに並列する5nFを外すと音は濁るが、450kHzで、そのとき電源電流は40mA以下であり3倍効果的で周波数3倍と理屈にあう。出力フィル タは、周波数が一定ならLC並列共振回路も考えられるが、周波数の変動と拡がりから鋭い共振は使えないと思う。また周波数も音質優先 の範囲内で、できるだけ周波数を高くするだけである。Lは電流が数A流せることが必要で、例えば数mHのような大きなLは直径数cmのトロ イダルコア巻き付けでこれを直列すればすぐわかるが高域に影響する。22μHは 1MHzで138Ω、8Ω負荷のLPFカットオフ周波数は58kHzだ から、これよりあまり大きいLは使えない。

Mos FET CSG 回路の基本周波数が余りに低い。130kHz から5.1kに並列の5nFを正常動作最小470pFに変更し出力のLを除去すると 226kHz になり高域の音質が少し向上する。しかし、どうして周波数の低いのか不明。コンパレータのコレクタ負荷2kを1kにしてもむしろ下がる。 低い周波数は消費電流削減の面はよいのだが、余りに低い。CSFの2MHz近辺と比べて1桁低い。負帰還抵抗分割を51k+5.1k//5nF〜1nFから 22k+2k//5nFにしてさらに10k+1k//5nFにした(//は並列)。+IN/-IN間のコンデンサを1000pFから470pFにした。出力のLは付けた。無音時 は220kHz程度で音量によって220kHzから4,500kHzに変化する。200kHzで十分とは思えず、1MHz以上にしたい。

非反転に比べて反転の発熱が大きいと明確に意識したのはBTLの2台目だった。非反転が2k+22kと5nFであり、反転は、5.1k+51kである。 測定するとVR位置によって周波数が変動し、非反転は 2.1-2.7と1.7-2.5、反転は 1.25-2.43と1.17-1.35 (-はVR位置による変化範囲)。 反転の方が周波数が低い逆転が理解できない。周波数カウンタ入力のコンデンサを200pF程度に小さくして測ると以前の測定と違って非 反転は4MHzで反転側は6.5-7MHzである。これなら反転側の大発熱が理解できる。音質は最高に透明で、高音の再現にはやはり1 bitアン プの周波数が高い必要があるようだ。発熱さえ解決すればこのアンプが一番ではないか。

TrのCEFによる1台目BTLの右コンパレータの電源GND間に0.1μFを2個追加、中点電位とGND間にも0.1μF追加して、右コンパレータ入力 +IN近辺の多くの空きランドを中点に接続して安定化したがノイズは消えない。そのときソースのCDプレイヤーを移動すると消える配置 があることをみつけ、またBTL1台目だけでなく、BTL2台目でも同様なノイズが出ることを確認した。これはつまり、ソースのCDプレイ ヤーが停止時に高周波を拾って出力しているのである。スピーカーケーブルからソースへの回り込みによる異常発振ならアンプ内部の 安定性の問題ではない。アンプが高周波を出さないように出力にLCフィルタを付け、BTL出力両端にLを付けるのは有効かも知れないし、 入力フィルタも効くかも知れないが、BTL1台目の雑音の問題は、こうしてほぼ解決したのではないか。

TrのCEFによる1台目BTLの発熱の解決を目指して、出力Lフィルタ22μHをBTLの両端へ付加し、Tr CEFの追加修正を始める。コンパレータ 負荷抵抗が750Ωだったのを 3kΩ+Tr CEF(2SA1015/2SC1815)にする。これによって抵抗の電流が減少し出力Trへのドライブ電流が増える。 2SA1359/2SC3422はコンパレータで直接ドライブでは安定的に異常発振なく動作させることが難しく、もう1段 Tr CEF をいれないといけ ないことを私はブレッドボードで知った。負荷が750ΩはhFE=100や200では7.5Ω〜4Ωでまだスピーカー負荷の出力抵抗として大きい。 出力の電流不足は発熱の原因になり得る。コレクタ損失は電圧降下と電流の積であるが、電流制限されても損失になると考えるべきだろう。

それまでのユニバーサルボードではなんとかして安定化させたのであるが、それは究極のコンパクト配置とコンパレータのpin5,6のVcc 接続での入力段の電流増加によって安定化が可能な範囲にあっただけである。一般に参考にしてもらうには難かしい回路だった。そこで Tr CEFを追加する。これが3kΩ+Tr CEF(2SA1015/2SC1815)である。また、BTLステレオの出力の負荷の両端に22μHのインダクタンスを付 けた。CDプレーヤーからの回り込みはなくなったし、電波放射は何に影響するか分からないから付けるのが正解だろうが、4個の22μHは 大き過ぎこれによって高域の音質がさびしくなった感じがある。L=22μHでは2πfL=4Ωになるfは29kHzだから、インダクタンスを約1/3、 5〜7μHにしてカットオフを100kHzに上げるべきか。Trの CEF追加とフィルタL付加の結果、無音時の電源電流170mAが105mA、このBTL1台 目の作成時当初の電源電流190mAから約半分にまで下がった。放熱板はTrの側を触って温かい程度(〜40°)である。これなら箱に密閉し ても発熱の問題はないだろう。また、出力ショート対策に電源(18V0.8A)に0.65Aのポリスイッチを直列した。

アンプとスピーカーが装着感や接触感がないのは当然だが、この音がどれほど理想に近付いたかは何ともいえない。しかし、少なくとも 私が昔から耳にしてきた音はこれほど良くなかった。ソースが変わったのではない。確かにソースが良くなって音が変わった時があった が、CDが出てからすでに数10年経過した。バックローディドホーンのスピーカー工作は、手と頭が伴う作業である点で確かに多少は私を 裏切らなかった。30mm合板を3、4枚くり抜いて一度も電気をいれずにそれが壊れていると知った私のダイレクトドライブターンテーブル。 レコード板、カートリッジとフォノアンプという道具立ては余りにも不便で不細工な代物だった。オープンリールデッキも低価格品の音 質は良くなかった。それほど音楽にもオーディオにも詳しくも深くもなくオーディオ技術に憧れるだけの貧しい学生に良い音が想像が付 かないというわけではなかったが、私の周囲の音は、1 bitアンプによってこの30年間から一変したと思う。長く中断したオーディオ熱 が再来した理由は、何年も自演するのが楽しかった2声と3声のインベンションのように、特にニ短調の半音階下降線(3声の4番)のような バッハの曲の素晴らしさである。最近ではキース・ジャレットの平均律のピアノ演奏を音を聞くのが楽しみになるような小型のアンプに よってG5のグランド・ピアノの両側に立てた能率だけはどれほどよいかいえないほどよい8cm1mの透明な点音源型の筒型スピーカーで鳴ら すと疲れは収まり、不可解な世の不条理な悲しさのなか、私はまだなにもしていないと気が付いて、再び歩きだすことができるような気 がするからである。

負帰還1bit アンプの音は、あっけない均一さをもつ。1台毎に個性があって、その間の違いを楽しむ面はない。異常発振による雑音 を抑えれば、ほとんど同じ顔になる。シングルアンプとBTLも出せる音量の違いだけで音質差はほとんどない。ケミコンを使うシングル ブリッジはケミコンの特性が音に出るが、スピーカーの逆端子のケミコン側を中点電位(コンパレータの基準電位) に帰還すればそれが 消える。基本的に音質差がないことが負帰還型1 bitアンプの特徴である。その長く聞いていられる音質は、かなり理想に近い。しかし、 異常発振による雑音が本当に消えているかどうかは難しい問題でこの型の1 bit アンプの基本的な欠点になり得るだろう。限られた耳 でそれを判断することは不確かであり、この種の雑音が回路構成上発生しやすいなら、そのことがこの型の1 bit アンプの基本的問題 となることも考えられる。どのようにそれが発生し、どのようにそれを防止するかを明確にすることが必要なのである。

コンパレータが電圧を比較して出力をON/OFFするのは理想化した動作であって、コンパレータは実は奥深く、今回使用したLM311はコン パレータのまだ入口であり、それよりはるかに高速なコンパレータがあって、それらを正しく動作させることは高度な技術を要するだ ろう。状態遷移の期間に通過するのは通常のアンプと同じ線形動作であり、遷移期間に安定でなければコンパレータは異常な動作をす る。そのときコンパレータは741型でなく709型の位相補償されていないOPアンプである。位相補償されたOPアンプはまだ電源間にコン デンサをいれ交流インピーダンスを低くするだけで理論動作が期待できるものだが、スルーレート(V/μS)が低く、低ゲインの動作では それを使うしかないが、高いゲインでは位相補償のない709型の負帰還を調整して高速動作を期待できる。無帰還のコンパレータは、位 相補償なしのOPアンプを最大ゲインで使うときの安定性に似ている。

1 bitアンプの負帰還は、普通の抵抗やコンデンサで出力から入力に返すHPFの負帰還でなくLPF型の負帰還だから、全体系はその逆特性 であり、カットオフ周波数以下は低ゲイン平坦、カットオフ以上は周波数に比例するゲインをもつ微分回路である。それはコンパレー タの高いゲインに対応する高周波まで続くから、負帰還コンパレータは異常動作しやすいのである。コンパレータがOPアンプ以上に難 しいのは、コンパレータに高速な遷移を望むとき高周波回路として扱う必要が強くあるからである。部品配置を改良し入出力を分離し、 浮遊容量などのLPFによって又は差動入力間にコンデンサをいれて素子の特性から離し、又は入力部分のバイアス電流を増やして高速化 し、素子の特性を上げて離して安定化する。差動入力間にクランプダイオードを使うのは、差動入力間の電圧は通常には微小であるが、 何かの原因で大きな差動入力電圧が発生するとそれからの回復に時間がかかるから、大きな差動電圧自体を防止するのである。

Trの負荷は1k+1kは最終電位(9v)が大き過ぎ1.5k+510(4.5V)にする。NFB 10k+1k//5nFの5nFを無くし+IN/-IN入力間のC=102(+471)だけに すると無音時周波数は200kHz程度から550kHzに上がる。Trの負荷1.5k+510では70mA、1.5k+270では49mAになり発熱少。pin5,6はVccのま ま(外すと却って電流増加)。2k+270にすると38,39mA。L(22μH)を負荷に直列し34mA。NFBを51k+5.1kにしてCは入力間の102にすると525 kHz。Tr 2SA1015を2SA950にすると周波数が995kHz 33mAに上がり周波数が約2倍になる。2SA1015のドライブ能力制限があったのか。周波 数は目標達成だが音が悪い。5.1kに並列の102で無音時350kHz53mA音は少しよい。並列Cを5nFにすると270kHz58.5mA音はもう少しよい。 入力間のC=102だけと並列5nFにすると310kHz-320kHz(VR:0位置)370kHz(VR:中位置)音質はよい。NFBへのC並列は周波数を下げるが音質を 良くする。ブレッドボードで音割れが残ってもユニバーサル基板で回復可能として995kHzをとるか、音量と音質のよい320kHをとるか迷う。

単純化のためCを入力間だけにする。非反転回路で入力VRから+INに直結し、中点基準にNFBの51k+5.1kの5.1kが結合するとき、+IN/-IN間 コンデンサは-IN中点間コンデンサとは入力信号が乗ることとVR抵抗が挟まることしか違わず、負帰還にとってほとんど同じである。5.1k を中点から入力VRに、+INを入力VRから中点に繋ぎ替え入力信号の符号を変えるだけで反転型回路になる。非反転も反転も同じ負帰還特性 である。入力間の容量は音質から5nFにする。+INから入力に又は中点につなぐ抵抗は省略し入力間C=102と-INと中点間のC=5nFは入力間C =5nFだけに変更した。

Tr負荷の2k+270は最終電位が2.14Vで34.5mA(L付き)、1.5k+270では2.75V,39.5mAであり、どちらにすべきか。抵抗を流れる電流の(TrON 時18/2=9mA,OFF時18/2.27=7.93mA平均8.41mAが、18/1.5=12mA,18/1.77=10.17mA平均11.08mAに)2.67mAだけの増加が全体で5mA増加である。 残りの2.33mAが貫通電流増加と思う。これぐらいは間のOFF期間を考慮すれば可とする。周波数は926kHzが945kHzに戻る。5nFを1nFにする と1.05MHzで37.5mAだが、ユニバーサル基板では1nFが可能かもしれない。Tr CEF のBTLでは1nFにできた。5nFで、コンパレータ負荷を270 +1.5k+270にした。N-ch最終電位をP-chに合わせ、17*0.27/1.27=3.61Vを17*0.27/1.77=2.59Vにする。987kHz 37.1mA(1nFでは1.15MHz35.0 mA,2nFでは1.05MHz 36.1mA)

ユニバーサル基板にCSGの4回路を組む。270+1.5k+270、1.5k+270、入力間5nFである。不具合は(1)電源電流(0.6-0.8A)で発見し、コンパレ ータをソケットから外し一個毎に入れ電源電流をみて特定したNFBの-INへの結合忘れ。(2)Tr負荷のGNDからの1.5kの半田付け不良。症状は 無音からぶつぶつ雑音。chとどちらのCEG端かを特定し、テスター導通によって 2SJ377gateとGND間の1.5kが10k程度を発見。半田少なめだ けで不良とは見えなかった。(3)異常発振で音が少し割れる。コンパレータ入力近辺で中点電位GND間に0.1μFの追加は効果が少ない。コン パレータの電源GND線を出力回路の電源GNDから分け0.1μFを追加しツイストペアにしてボード入口の電源GNDに結合。タンタルコン3.3uF35V を出力の電源側に2個いれたが雑音が残る。(4)L(22uH)4個を各CSGに付けるが音がなまるだけで外す。(5)ツイストペア化のときLM311の電源 を逆に繋ぎ、(赤黒線は間違えようがないが付ける側に目印がなかった)、電源電流が各5mA増加し音も悪化。LM311の4個を交換し回復した。 シングルでは4回路とも正常でBTLで雑音がある。(6)片chだけ5nF=>1nFにして+INにも5.1kをいれるが雑音は増加した。

(7)コンパレータ電源GND線のツイストは効果があったが、基板上の出力線の両端ツイストを試したが有害らしく解く。同chの出力両端のツ イストは、音響では逆相だがパルス波形は独立だから干渉になる。(8)各出力CSG電源GND間に0.1μFを追加。雑音は両chに漂うが1nF側から が大きい。入力ミニジャックを外してVRを回すと、ある位置でヒューという小さなノイズが出て、戻すときはその位置で出なかったりする。 この異常音のあるときBTLなのに電源ON/OFF音がある。これは今まで何度も経験し、その都度対処した一般的な1 bitアンプの異常発振の症 状だが今回は結構難しい。それは回路自体の無理さ(強引さ)加減の問題だろう。Tr CEF, Mos FET CSFではもう少し素直に問題が収まった。 シングルで正常でBTLで異常というのはCSG回路間やch間の干渉を意味し、電源GND間のコンデンサ追加の効果が期待でき、ノイズ源の出力 回路の電源GND間に高周波特性のよいコンデンサをいれ、ノイズの受け側のコンパレータ入力信号線にシールド線を使ったり、時定数CRが オーディオに影響しない程度のコンデンサも許される。結果的にコンデンサの数は問題の深刻さを表す。対策は実行してみて初めてそれが 有効かが分かる。有効なら残し無効なら戻す。回路を複雑にする修正は必要最小限にする。原因に当たらない対策はいくらしても無駄であ る。ほとんど不可能に思えるようなひどい音も、その音自身が解決を要求し続けるから、なんとか有効な対策を見つけるものであるが、対 策の作業量が多過ぎると考えるならその回路を諦めるしかない。(6)は戻した。(9)VRからの入力にシールド線を使用。(10)クランプダイオ ードを試すが解決せず外す。(11)(8)で余分につけた0.1μFx4,5nFx4を外す。

また、別の見方でいうと、出力の内部抵抗は、出力の負荷抵抗8Ωより十分低くしたい。ダンピングファクタ(負荷抵抗/内部抵抗の比)を10以 上にしたいが、1kΩ負荷の1/h_FEは、h_FEを100とすると10Ωであり、それができず、明らかに大き過ぎる。しかも、h_FE は大電流で下がる 傾向があり、2SA1359/2SC3422(40V3A)の0.5Aのh_FEは80〜240だが2.5Aでは25〜である。 (大電流のh_FEには 2SA1931/2SC4881(50V5A)は、 1Aで100〜300(2SCは320)2.5Aで60〜、2SA1887/2SC5000(50V10A)は1Aで120〜400である。)

その問題は、出力回路をTr CEFの2段縦続接続にして、合成した電流増幅率が縦続した h_FE の積になること、1段目100倍程度と2段目数10倍 との積、数1000倍によって解決する。これはTr CEFによるBE間の0.7Vの無駄電圧の追加を考慮しても価値がある。しかし、正確にはこれで解 決でなく、2段Tr CEFでも必要な1mA〜数mAで1V〜数Vの電圧降下はまだ大きい。そうかといって、1kΩを下げるとコンパレータ LM311の出力 電流の限界(50mA)に挑戦することになるし、ステレオBTLではその回路を4つ使うから、この電流による無音時発熱の増加は避けたい。1kΩ時 の36mAさえ減らしたいのである。Mos FET CSF 回路では、この1kΩを2kΩにして電流を半減したが、電圧降下が2倍になるのは問題である。

抵抗では電圧降下が電流に比例するが、Tr や FET の電圧は電流に比例しない。Tr の Ic-Vce 特性の曲線の平坦部分は定電流特性であり、 そこでは微小な電流変化に大きな電圧変化が伴い、素子の定電流特性と負荷の定電流特性と合わせれば電圧利得が大きくなる。定電流特性 をもつ負荷は定電流特性をもつことに伴い、0Vの近くに曲線の折れ曲がる肩をもち、原点からその肩までは低抵抗特性である。これをVcc からの電流源に使い、例えば2.5mAの定電流負荷ではHighレベル時2.5mAまで電流を取り出しても電圧降下はVceの0.数Vに縮小でき、肩を越 えたLowレベルまで定電流性によってほぼ2.5mAのままで、無音時の4回路の消費電流は10mAに削減できる。スイッチング素子に定電流負荷を 使う意味は、素子OFF時の飽和と低インピーダンス性電流供給、遷移時の高利得、ON時の低電力である。素子の及ばないOFF時の特性を定電 流負荷は改善できる。TrよりFETはさらによいはずだが、2端子の定電流ダイオード(CRD)は、高耐圧(100V)を狙って肩の電圧が小さくない。

下図は、(a)はこれまでの抵抗負荷である。抵抗負荷では、電流変化は抵抗倍されて電圧変化になる。電圧ゲインを確保したいなら、高抵抗 を使いたい。そこから電流を供給するなら低抵抗を使うしかないがゲインは低下する。両者を加味して抵抗値を決める。出力Tr CEF へつな ぐとき1kΩ〜700Ωを使用した。High レベルはこの抵抗を通して出力Trのベース電流を供給するから、High レベルの電位確保が難しく、 できるだけの低抵抗を採る必要があった。だだし、2段Tr CEFのときはより大きな抵抗値を取ることができた。

(b)は定電流負荷である。定電流は高抵抗負荷に対応してゲインを確保できるだけでなく、制御Tr OFF時のHigh レベルの負荷Trの肩による 低抵抗を用意する。制御Tr ON時には、その定電流値が制御Trに流れ込むが、低抵抗負荷による電流ほど大きくする必要がない。High レベル 時に負荷Trから引き出す電流だけでよい。

さらに、考えられる図34(c)のON/OFF負荷は、制御Tr ONのとき下の反転TrがOFFになり、それを負荷TrもOFFになり、制御Trに流れ込む電流 をなくす。制御Tr OFFのとき(*)はその逆で、下の反転TrがONで上の負荷TrをONとして導通を確実にして、High レベルを高くする。この回路は 状態遷移にしか電流を消費しないのでドライバ段の低消費電力化になる。出力Trが互い違いに帰還するフリップフロップのようになって、 その負荷がTrでつねに反転する、(d)ON/OFF反転ブリッジ出力回路が欲しいが、この出力ブリッジは入力Vcc/2時貫通電流があり危険である。 (166kB 12/3 2009)

*図34(c)のON/OFF負荷は、制御TrがOFFに変化しても負荷がOFFなので反転Trにベース電流を流せずONできない問題があるが、ON/OFF負荷に 高抵抗を並列して、上から常に少しの電流を注入すれば、動作は可能である。

図35(a)の回路は、図34(c)ON/OFF負荷回路の反転Trを出力Trの下側で兼用したもの。動作は、最初、出力がHighとする。コンパレータ出力 がONからOFFに変化する。このとき負荷TrはまだOFFである。上下OFFになると、両コレクタ電位は上がる。それによって出力Trは、下がOFF からONに移り、上がONからOFFに移る。それによって出力端の電位は下がる。これを帰還する負荷Trのベース電流は増え、負荷TrはOFFから ONに変化する。それは上がりかけたコレクタ電位を更に持ち上げる。正帰還は、帰還ループ中の電位変化をその方向に進め、逆側(出力Low) への変化を後押しする。それは2極化であり、遷移を確実にし高速化する。図34(c)のようにループに出力Trを含めずに途中から返すと、 ドライバ段の反応は速いが、帰還ループの外の出力Trの変化は、高速化されないだろう。

しかし、図35(a)には問題がある。Tr2,3の各ベース電流のh_FE倍の電流がCE間に流れ得るが、LM311とTr1が両方OFFのとき、Tr2のベース電 流がTr3のベースへ流入し、それぞれのh_FE倍のコレクタ電流の貫通が、最大でVcc/2R、最大出力電流の半分もある危険な回路である。 図36(a)は、ZDによって変化する電位の振幅を縮小し、rを低抵抗にするが、やはり、(Vcc-Vzd)/rがベースを貫通する。 対策は、図36(b)のように、2個のツェナーダイオード(ZD)(Vzd≧Vcc/2)を両ベースに直列することが考えられる。上下ドライバがONとOFFの とき、ZDを1個を通る (Vcc-Vzd)/r のベース電流があるが、両方OFFでは両ZDを経由するベース電流は、両ZD電圧の和が電源電圧以上なら、 流れない。

しかし、図36(c)には貫通の問題が残る。Mos FETのドレイン電流の貫通は、図37のように、上下Mos FETのゲート電圧の交差によって決まる。 下の N-ch は、Vgsが Vth でドレイン電流Idが1mA流れ、その2倍の2Vthで十分な電流が流れるとする。上側の P-chは、電源電圧Vcc-Vthの ゲート電圧によって同様に1mA流し、その2倍の2Vth下がった電位で十分な電流が流れるとする。両者は上下対称で、両方のゲート間電圧を "電圧シフト" のツェナーダイオードによって固定すると、上下のゲート電圧は連動して平行移動し、両図を重ねた右図のようにドレイン 電流の交差によって、流せる電流が考えられる。貫通ドレイン電流は、右図の2本の電流の最小値(2本の線の下側)、ゲート電圧Vgsの関数と しては Vgs= Vth のとき最大1mAになる。

この交差電圧を閾値電圧にすると、1mAの貫通に収まり、閾値電圧の2倍で十分ONになればよいが、実際はそれほどうまくいかず、十分に流れる ON電圧に達しない。十分流そうとしてVzdを小さく振幅を大きくすると交差電圧がVthより大きくなり貫通が大きくなる。特性として欲しいのは、 閾値電圧の2倍程度で十分なONである。例えばONで2.2A流れて中点で数10mA程以下の貫通なら許されるだろう。時間平均の貫通電流なら10mAでも 避けたいが、これは遷移であって時間平均の貫通電流はそれより1桁小さいだろう。2SJ377/2SK2231や2SJ380/2SK2914のデータシートでは 1.5V とその2倍の3V (Vzd=Vcc-3V) ならON電流不足ながら何とか動作しそうだ。しかしこれは妥協的設計であり、閾値電圧とON電圧の2倍以内の関係 が確かでないこと、設計の要が電源電圧とツェナーダイオード電圧との差に依存し、電源電圧を変えられない、Mos FETとZDの素子バラツキに弱 い設計であり、最終的な解決ではないと思う。

ツェナーダイオード(ZD)は、順方向は通常のダイオードと同じ0.6V低下して導通し、逆方向にはVzdだけ減らして導通する。図38のように2個の ZD(Vzd≧Vcc/2)を両ゲートに直列する。Tr CEF用に考えた図36(b)と同じく、1個の直列ZDは導通し、2個直列ZDは導通しないことを使う。この 回路は、12VのZDを使って広い電源電圧(16V〜24V)で動作する。Vcc=18Vでゲート電圧6V、Vcc=24Vでは12Vを与える。Rの上側のドライブ電圧 -12V(=6V)以下でP-chゲート電圧がドライブ電圧に追従し、Rの下側の電圧が12V以上でN-chゲートが追従する。間の6Vの幅の不感帯(Vcc=16Vで 幅12V、Vcc=24Vでは不感帯なし)ではゲート電圧はZDの微小電流の電圧範囲(-12V〜+0.6V)で高抵抗である。そのときGS間の抵抗rは、Mos FETの OFF化をする。GS間電圧を4Vに制限するZDも考えられるが不要と思う。負荷TrON時のベース電流が制限しない限り、Rはドライバ上下同時ON時の 電流を決める。例えば、R=r=270では常時11mA、遷移時のドライバ上下ON時にVcc=18Vで66mAは少々大きい。R=rではON電圧3Vであり、r<Rには できない。

気が付いた問題点があって、コンパレータがONからOFFに変化し一瞬ドライバの上下がOFFとなっても、Mos FET出力は、上ON下OFFから変化せず、 ベース電流源のない負荷TrはONに変化しないのである。出力素子はループから外すべきか。図34(c) のように別に反転Trを介して負荷Trに帰還 すれば、ON/OFF負荷は可能なはずである。

Rは必要である。出力素子をドライブするためにコレクタ電流には余裕がいる。そのため負荷Trのベースに余分な電流を与えON時にコレクタ電流 を十分供給する。ベース電流によってそのh_FE倍のコレクタ電流を制限すればよいとRをなくすと、この余裕電流まで全てが下の素子に流れる。 ON/OFF負荷Trに大きな余裕電流(例100mA)をもたせ、遷移時に下のコンパレータがONになると電流を制限するのはRだけである。R=600Ωとすると 6Vで10mA、上下ON時に18Vで電流を30mAに制限する。

rは必要でない。Mos FETのGS間の抵抗r=∞ならドライバの上下コレクタ電流はON/OFF両状態において流れず、遷移時以外は電流が流れない。 しかも、12VのZDはMos FETのGS間に完全な差の6Vと0.6Vを用意する。何か漠然とハイインピーダンスの危険を感じて抵抗rを使うと、r=Rでは GS間電位が半減し、電流が常に流れ、それはもはやON/OFF負荷でさえない。rがなくてもZDは電圧を制限して高抵抗を排除し微小電流の電圧範囲 を使わない(図39 参照)。遷移時には確かにゲートは浮動状態だが、そのときMos FETの入力容量(2SK2231で370pF、2SJ377で630pF。大電力用Mos FETはもっと大きい。) のゲート電荷が移動しないだけである。

ゲート電荷の移動なしに電圧は変わらない。遷移時にゲート電圧の変化は必要と思い、遷移時にゲート電荷が移動しないと言うと、矛盾と思う かも知れないが、遷移の詳細をみると、図39の遷移の瞬間t0とt1にx1とx2は変動せず、変動しているのはx3とx4である。遷移後のMos FETの ゲート電荷を消すOFF化は、ドライバのコレクタ電流によって速く起き、ゲートのON化は、ゲート容量cへのRを通した電流によって、ほぼ時定数 (cR)時間を要して起きる。

t0にLM311がONになると、まず、N-chゲートからZD順方向を通してLM311への流入があり、これがN-chゲート電荷を消し、N-chをOFFにする。次に 負荷Trが帰還を通してOFFになりコレクタ電流が消え、CE間電圧が広がり、x1,x3間が12Vになり、ZDが逆電圧導通しP-chゲートからRとZDを通した LM311へ上からの電流の流入がある。これには時定数(cR)時間を要して P-chの負のゲート電圧を蓄積し、P-chをONにする。

t1にLM311がOFFになると、まず、両ドライバOFFでゲート浮動になり、そのときP-chは、ON(N-chはOFF)のままである。次に帰還によって負荷Trが OFFからONになり、そのコレクタ電流がZD順方向導通でP-chゲートに流入し、電荷を消散してP-chをOFFにする。また、同時に負荷TrONによってx3 電位が上がり、負荷TrのコレクタからRとZDの逆方向導通 (x2,x4間が12V)を通し、時定数(cR)を要して、N-chゲートに電流が流入し、ゲート電位 を上げ、N-chをONにする。

コンパレータLM311が起こす遷移は、LM311のONからは、すぐ起きる出力のN-ch OFF化と、帰還による負荷Tr変化と時定数による出力P-chのON化が 伴う。LM311のOFFからは、すぐには何も起きず、帰還による負荷Trの変化によって、出力のP-ch OFF化と、時定数による出力N-chのON化が伴う。 このとき、帰還による負荷Trの変化が来ないと出力のMos FETの上下がOFFのままであることは、反転Trで負荷Trへの正帰還ループ(出力素子を含 まない局所ループ)の必要性を示している。両方の遷移ともOFF化よりもON化を時定数だけ遅くして貫通を防ぐ。

図34(c)のON/OFF負荷は、LM311がOFFで負荷がOFFなので反転Trのベース電流を流せずONにできない。ON/OFF負荷がLM311 OFFへの変化を外に隠す。 しかし、LM311のON/OFF負荷に高抵抗を並列し、上から常に少電流を注入すればLM311OFF時にベース電流が反転TrON、負荷TrONにできる。 LM311 OFF変化時に高抵抗でx3,x4を上げても、すぐには出力Mos FETは反転しない。出力からの帰還でなく、図34(c)の反転Trがいる。

定電流負荷のほうがON/OFF負荷よりも単純さにおいて勝るかもしれない。定電流負荷では、ドライバに一定の電流を要し遷移を高速化しないが、 出力段の遷移に疑問はない。余裕電流を大きくし実電流を制限するRは有効だろう。PNP Trのベース電流のh_FE倍を10mAとすると、コンパレータ OFF時(図40左)に、P-chの負電荷をZD順方向でOFFにし、N-chをRとZDを通した電流でONにする。両電流の和は10mA。コンパレータON時(図40右)に、 N-chの電荷をZD順方向でOFFにし、P-chをRとZDを通した(10mAに制限されず Rによる)電流でONにする。

OFF期間に両入力容量へ流入し、ON期間に流出する"ポンプ電流"と、その間も一定に流れ込む10mAとの和がコンパレータ電流平均20mAである。 全電流の平均は10mAであり、RとZDを通す電流は両chのON化の時定数を決め、OFF化ON化の順が逆転すると貫通だから検討がいる。大きいRでは 逆転はないが周期が長くなる。R=0ではドライブ電圧が12V+0.6V以上でN-ch ON化、Vcc-ゲート電圧+0.6V以上でP-ch OFF化する。閾値2Vでは電圧 上昇途中、14V以上でON化、16.6V以上でOFF化、と逆転している。

Rで上下を分離し、Rの時定数でONを遅延させるのは基本方針である。2.6Vの差は、R=270Ωに10mA で防げる。しかし、貫通をレベルで防ぐには どの直流電圧でも上下ONにしないことである。Vzdを調整するならVcc-Vth+0.6V<Vzd+Vthは移項して Vcc-Vzd+0.6V<2Vth。これは、図36(c)に でた、ON電圧は閾値の2倍まで、という関係で、ZD順方向0.6Vがさらに難しくする。Rの代わり数VのZDかLEDをいれてもよい。

その点、ON/OFF負荷は、貫通がない。LM311がOFFになると上下のドライバがともにOFFになって、上の負荷Trが帰還によってONになるまで出力が 状態を変えず、Rは必要だが、RにZD追加の必要はない。局所反転Trのベース電流を与える高抵抗は要る。LM311がONになるときもドライバ上下ON になると、Rがドライバ電流制限に要るが、帰還によって負荷TrがOFFになるまでは、下のN-chがOFFになって出力上下OFFになる。ふたつのZDも 不要ではないか。ZDは遷移中の中間レベルを出力OFF化する。ZDなしのLM311ON時はドライバ上下ONで不要で、OFF時は上下OFFで浮動するが上か ら高抵抗で吊るからよい。ZDの使用はもちろん可能である。

ON/OFF負荷のよいことは、定電流負荷が電流を最小化しなければならないのに対して、ON/OFF負荷はポンプ電流以外流れないから余裕電流を大 きくできる点、そして、遷移の正帰還による高速度が期待できる点である。定電流負荷の抵抗負荷に対してよい点は、Highレベルの低抵抗が得 られることである。定電流負荷ではZD付き、Rの代わりのZD付加も必要だろうが可能だろう。ZD負荷回路も動作可能であろう。さすがに抵抗負荷 ではCSG動作は難しいだろうが可能かもしれない。CEFやCSFは単純な抵抗負荷で動作できた。CSGのZD負荷、定電流負荷、ON/OFF負荷の回路追求は、 CEF, CSFよりも小消費電力で高周波数動作できる等の明白な利点を必要とする。

LM311 非反転回路 pin5,6間結合のみ。負帰還は22k+(2k//5nF)。+IN/-INに1000pF。Rb2=51k,5.1kの抵抗分割。出力スピーカーに直列に22μHのLを 使った。TrのOFF化にシャント抵抗5.1kが必要。Tr1のコレクタ負荷R=270Ωでやってみた。ZD12V 2本。出力Tr(2SA1359/2SC3422または2SA1887/ 2SC5000)では、ブレッドボードに組んでTr発熱大で、匂いで気づくまでにTrの足をさしたブレッドボードの穴の周囲のプラスチックがとけ、Trを 触ると火傷しそうなほど発熱していた。TrのBE間にOFF化抵抗rが必要で、R=r= 270 にしたが依然、PNP側の発熱があり、R=1kにして大発熱は収ま った。

その回路をrだけ外して Mos FET (2SJ377/2SK2231) の動作を確認した。電源電流はまだ大きいが発熱は大したことはないと思って、触って確認 をしながら電気をいれたP-ch側でなく、N-ch側を触ったとき人指し指の皮膚を白く火傷した。指を1時間ほど冷やして翌日、電源電流を確認する と0.3〜0.4Aと大きい。P-ch側のゲートソース間に1kΩの抵抗を並列すると電流は正常(50mA〜60mA)になる。これなら長時間でもMos FETは温かい 程度である。N-ch側のGSにも1kΩ並列を試すと良好で(R=r=1k)、さらに3本の1kを270Ωに変更(R=r=270, (46?)56mA)。VR最大で入力からの高周波 の回り込みらしき異常音が聞こえ、VR,-IN間に5kを入れる。異常発振の雑音が混じって、音質があまりよくない。

図43(c)も同じ性質で音量が小さくVRを上げるとバリバリ音が出る。電源ONから数秒80mA程度流れ、小さくパチと音がして電流が60mAに下がって音 がでる。R=100Ωにすると少し音量が上がるが大して違わないので戻す。Rとrの比のようで、下側の270Ωを取り去り、上のrを2kΩにすると(上のr もなしでは電源ONの大きな音以外音がでず電流は小さい) かなり音量は上がったが十分ではない。VRを一杯に上げると音の大きいところでバリバ リ音がでる。これでR=100Ωにすると電流150mAから下がらず、Rが熱くなるので戻す。LM311出力に触るとビーという音が出て正常でないことが分 かる。よくこんな状態でこれほどきれいな音が出るものだと感心する。下のrを外したときから小さなノイズが混じるが、前のようなシングルのス ピーカ逆端の中点への帰還なしにこの音は貴重かも知れない。動作中電流は60から70mAに増加。Mos FETは冷たいままである。

上のr=2kを変えて最適値を大雑把に知りたい。1kにすべく手近にあった2kを差してまだ何の調整もしていないからである。最適なのは500〜1kΩか と思ったが違った。270Ωでは明らかに小音量でバリバリ音。1kでも出せる音量が下がる。逆に抵抗を上げると5kΩ,10kΩはかなりよい。22kΩでは ピーという大きな異常音。5kの大音量時の雑音はまだバリバリ音で、10kはクリップ音に似た少しだけ異常な音である。VRを少しだけ下げれば正常で 一番ましである。BTLステレオでは電源18Vのシングルモノラル18x18/64=5Wの8倍出せる。しかし、実際のMosFET CSFのシングルモノラルの回路に戻 してCSFより明らかに小さいと分かった。CSFの電源電流はLM311の負荷抵抗5k-1kで無音時35-40mA程度である。CSFは電源ONですぐにパチと音がして 音楽がなる。上の回路では電源ONから数秒(2秒)後にバリと異常音がしてから正常な音がなり出す。これがまず問題である。最初の数秒と音が出て 以降とは電源電流が異なる。出力電圧が数秒で0V〜Vcc/2に上昇する。上昇中、負荷Trの5kのベース電流でケミコンが充電され、LM311がONなのに負 荷TrもONで、上下のMos FETがOFFである。出力とVcc間に1kを付ければこれは短縮するが、電流10mA無駄だし、音の出始めの雑音は残る。また、BTL ならケミコンはないから、この数秒の時間は全くないかもしれない。

半導体は絶対最大定格を越えないだけでなく余裕を持たせないといけない。半導体の発熱はその寿命に影響する。抵抗やコンデンサは、誤差があ り経年変化は大抵誤差を広げるから精度を必要とする使い方は避ける。ケミコンは容量抜けし、巻き線抵抗は焼ける。ゴムは劣化し、塩化ビニー ルは硬くなる。そして部品には数年で埃がかかり放熱が塞がれ、高圧を使うと埃に電気が流れそれ自身が発熱し発火する。低電圧はそれを防ぐ。 発熱は機器の箱の内部に対流を考える必要が出て、上に穴を開けるとコーヒーやスープが入る危険が伴う。複雑な操作が必要なものは必ず誤操作 される。どんな誤操作も事故を招かないように機器はフェールセーフにする必要がある。最後に機器は、使う人にとって美しくないといけない。 デザインは機器の機能と存在を示し、適度な大きさと形が大事である。それがユーザにとっては最後でなく最初に接する印象を決める。しかし、 ユーザが使って最後に感じるのは設計者の最初の設計である。

設計者が単純さを選ばなくてはならない理由のひとつに、複雑な回路や機能は機器の一生の間に一度も使われないか、ずっと不適切に使われるこ とがある。アンプにボリュームはどうしても必要だが、左右のバランスは部屋のなかで聞く位置に合わせるよりも、スピーカーを対称配置すべき であり、そうしないと聞く位置の制限が却って厳しくなり、その位置以外ではアンバランスな音を聞くことになる。

トーンコントロールやラウドネスも必要性が疑わしい。例えば、低音に弱いスピーカーに低音増強をしても低音が出ないスピーカーは、コーン振 幅制限があるためか、バッフル(前後の音の遮蔽)洩れのため低音が出ないのであり、コーン振幅を必要とする低音を増強して与えてもスピーカー に無理をさせるだけで(例えばTVの音質調整で低音増強は効果があるだろうか)、却って中高音の品質と音量を落とすことになる。低音にはコーン 面積とコーンの移動ストロークの積(体積)が必要で、口径8cmの1cmのストロークの低音は、口径10cmの6mm、口径16cmの2.5mm、口径32cmの0.6mm、 口径64cmの0.15mmで出せる。大口径には余裕に出せる低音が小口径には限界的なストロークを必要とする。ストロークはスピーカーの磁気回路と コイルの配置、そしてコーンの動ける範囲によって決まる。

音は媒質速度と音圧によってできているが、音の波の時間に伴った空間的広がりを考えれば、小型スピーカーからの音も大型スピーカーのサイズ の断面積の閉曲面を通過する。ここで音は発散(生成消滅)のない空間にあるベクトルに、流束は断面積と音の大きさ(流束密度)の積のように見る。 音の強さ、音響の信号波形は光と同じく距離の2乗に反比例し、それは断面積に反比例している。信号波形はコーン振動の振幅ではなく、振幅の微 分(コーンの速度)であり、同じ振幅では周波数に比例する。逆に振幅は信号波形の積分であり、同じ信号では周波数に反比例する。周波数が2倍な ら振幅が1/2で同じ音量(音圧や粒子速度)の電気信号波形をもつ。等しい振幅の電気波形を与えても周波数が1/2倍の低音では振幅が2倍になる。ス ピーカーコーンの振幅制限があるとき、アンプによる低音増強はその制限を回避できず、他の中高域を下げる効果しかない。

周波数特性を自由に調整するグラフィックイコライザの必要性はさらに認めにくい。グライコの調節の周波数範囲はどう決められたのかさっぱり 理解できないし、明確に効果を発揮できた例がない。周波数特性の調節よりもインパルス応答を自由にする方がどれほどか理にかなっていて、イ ンパルス応答の先鋭化処理によってできる平坦な周波数特性は、周波数特性を単に平坦にするよりもはるかに正しい。室内残響を除去し、CDの録 音状況で付け加わった残響を除去し、別の残響を付加するようなディジタル信号処理は、インパルスの先鋭化でできるが、周波数の平坦化では できない。

アンプにリモコンは欲しいかも知れないが、昔はなかったからと我慢する。それは単に一歩ないし数歩踏み出すことを避ける利便である。アンプ が小さく軽くなると気軽に手元に置いてアンプとスピーカーの間を数mのケーブルにすれば、人とアンプの間隔をとる必要もない。スピーカー間は 間隔が必要だからアンプを手元から壁際に移しても、スピーカーケーブルはそれほど短く、例えば半分にはできない。それはまだ手元からアンプ にリモコンで伝えるものは電源ON/OFFとボリューム制御だけである。そうでなく、逆にスピーカーとアンプ一体にしてケーブルをなくし信号経路 を長くする方向があり、そのケーブルを無線、光の変調、無線LAN、電源LANや UWBによって伝達し、室内を無配線にして室内デザインを自由にする。 しかし、高品質オーディオ信号を伝達するという問題があるだけでなく、スピーカーに電源が必要になる。無線LANや Bluetoothは電子レンジが 同帯域にあって雑音になる。また、数万円の複雑なディジタル回路が、数百円の信号線に勝てるかという疑問がある。

この場合、ケーブル抵抗がスピーカー抵抗に直列の同程度の大きさになって音量が下がる現象がでる前に、ダンピングファクタ(DF=アンプ出力抵抗 /スピーカー抵抗)というスピーカーの電気動力学的特性が変化して、電気信号によるスピーカーの制御が甘くなり、直列抵抗をいれたと同じく、 インピーダンス(抵抗)ー周波数特性に基本周波数f0のピークとスピーカーコイルのLによる高域のインピーダンス上昇を反映して、制御の弱い低域 増強と高域上昇のいわゆるドンシャリ音になる。スピーカーは電気信号を音響に変換する目的をもつが、アンプはそのコーン運動をドライブし、 コーン紙とその面積分の空気の質量と支持系のばね定数は、共振周波数f0をもつ機械振動系をなす。アンプからみたスピーカーには電気特性に機械 音響特性が表れ、支持系の軟らかさ(コンプライアンス=1/k(k:ばね定数))がコンデンサ(C)に、質量はインダクタンス(L)に対応し、両者は並列共 振回路をなす。インピーダンスピークを示す共振周波数は、バスレフスピーカには2つ、筒型スピーカーには多数ある。

スピーカーは、基本的にそれを駆動するアンプの出力抵抗を0Ω(定電圧駆動)として設計や測定がされる。このとき、運動はよく制御され、輪郭の 明確なきっちりとしまった音になり、アンプに出力抵抗があると制御が甘くぼんやりした音になる。定電流駆動するとインピーダンス特性に比例 したゲイン特性になる。アンプには負の出力抵抗も可能で、回路の銅線の抵抗の影響を減らすことができる。当然ながら8Ωスピーカーに接続する アンプは-8Ωまで安定でそれ以上ではインピーダンス最低の周波数で抵抗が0になって発振する。アンプの基準は0Ωであるが最適なDF値は10程度 と言われ、8Ωのスピーカーに1Ω程度のケーブル抵抗は有害ではない。

スピーカーケーブルには細い電線が好まれることがある。抵抗の直列によるDFの効果によって得られる軟らかい音質とスピーカーのインピーダンス ピークに対応した低音増強と高域増強は、ある程度まではそのほうが自然に感ずる面があり、直径の細さがインダクタンスを大きくする影響もある。 少し離れると見えないような細い線はひとを驚かすが、スピーカーの8Ωのような低インピーダンスでは普通に発生する数Aによって直径1mm程度の 被覆線は規格上耐えられる限界を容易に越えるのを注意すべきである。たった片ch16Wの8Ωのスピーカー用ケーブルには2A流れ、200Wの電気製品 のACコード程度の太さがいると考えられる。32Wで4A、64Wで8A、100Wでは12A、1.2kW。アンプ出力の12.5倍(4Ωでは25倍)である。

ところが、ダーリントンTr 2SB1226/2SD1828(秋月2組250円)を試すと問題なく動作した。BE間抵抗が前段にもあって(6k+200)、それらがよく調節され ているからだろう。電源電流0.04Aで動作周波数も独立2段CEF1MHzより高く1.3MHz。ダーリントンTrは、名前が2SBと2SDで高周波には無理だろうと敬遠 していたが、単一の高h_FEのTrのように扱え、2段CEFより回路の単純さで勝っている。これを真似て5k+270にしてみたが、電流が0.15Aあってよくない。

2SA1887/2SC5000は、BE間抵抗を51Ωにすると79mAで音楽は出るがぱちぱち雑音がある。25Ωで50mAでも雑音が消えない。2SA1931/2SC4881では51Ωで 45.4mAで動作、100Ωでも45.8mAで動作した。270Ωは85.3mAあるが動作できる。2SA1359/2SC3422では51Ωで44.4mAで動作、100Ωで45.7mAで動作する。 270Ωでは51.5mAで正常に動作する。Mos FETの2SJ377/2SK2231もCEF+CSFの39.5mAが270Ωで102mAで100Ωでは41.0mAで、51Ωでは39.2mAで動作した。 ここでいう"動作"とは、シングル(BTLでなく)でケミコン付き1bitアンプらしく大音量で聞こえることを数秒確認したことをいう。しかし、2段独立CEF は安全で調節不要なのに、ダーリントン接続は抵抗調節が必要で、CEFのインピーダンス変換の性能を落とすから、そうする利点がない。

それに対し、エミッタフォロア動作の逆転ダーリントン接続には多少の利点がある(図46(b))。1段目NPNの後に2段目はPNPをつなげダーリントン接続 ではベースエミッタBE並びが直列で、1段目のエミッタ電流を2段目のベースに入れるが、逆転ダーリントン接続では1段目のコレクタ電流を入れる。 ともに1段目が2段目のCB間に電流を流し、2段目は増幅するだけだから、全体として Trが1段目の極性(NPN)で、合成のh_FE= h_FE1*h_FE2 積になる のも同じ。しかし、2段CEFやダーリントンではBEの向きが同じだからBEの0.7Vは直列で1.4Vの無駄電圧になるが、逆ダーリントン接続では2段目のBE は1段目のCEに逆向きに繋がって隠れ、全体のBE間の最小の電位はVbe0.7V+Vce0.2V=0.9V程度に減る。なお、Mos FETでも同様に可能である(図46(c))。

回路を組んで電源を投入する(電源SWを10A電流計でショート)。予想どおり電流は0.12A程度。しかし音は出ない。出力が電源かGND電位に固定してい る。全体の動作が負帰還でなく正帰還である。接続が全体としては上側は1段目のNPNで、CEFをなし、反転しないはずが実際は反転していて、LF311の +INと-INを入れ換えれば、なんとか動作する。このとき電流は0.2A〜0.25A流れ、Trが温かい。極性がなぜ逆か、とよくみると回路が図46(d)であった。 これでどうして動作するのか不思議なくらいの回路である(*)。

訂正した図46(b)は音は出るが、最初0.13Aぐらいの電流がシャーというノイズがでて0.35A流れるから電源を切る。BE間抵抗を51Ωにすると0.11Aで 動作するが雑音が混じる。抵抗100Ωのまま2SA1359/2SC3422に差し替えると、電流が40mAでよいが音が濁る(大音量が出ない)のは足配置が違うため 起きたBE逆の誤り(**)。回路を訂正して50mAで正常音。270Ωでも65mAで正常音。Mos FET 2SJ377/2SK2231への差し替え(図46(c))は、100Ωは0.15A で放熱板なしの2SJ377は発熱し、高音に異常がある。270Ωは0.32Aでだめ。51Ωでは0.10Aで正常動作。10Ωで44mAで正常動作に近いが大音量で歪み。 20Ωでは64mAで正常。15Ωで50mAで正常。2SA1931/2SC4881は100Ω70mAで、51Ωでは65mAで正常音。最後に、2SA1887/2SC5000は、BE間抵抗で10Ωを 試せば56mAで動作した。

(逆転)ダーリントン接続では、大電流用Trは、BE間に低抵抗を付けないとOFF化が遅く電流が減らないが、それはベース電流をバイパスし電流ゲイン を低下させるから、抵抗値は調整する必要がある。無音時50〜60mA(18V)程度では温かくならないが、電流の違いは貫通が原因と思われる。最大音量 時にはシングルでもずっと大きな電源電流(18V8Ωで5.06W, 0.277A)であり、無音時の電流の違いは小さいが音楽の時間の大半は無音かそれに近い小 音量である。発熱が小さければ無音時に冷却でき熱設計を楽にする。常に最大音量が続くという設計では放熱板が巨大になる。ダーリントン接続CEF では最小45mA、逆ダーリントン接続CEFでは、最小が2SA1359/2SC3422の51Ωの50mAである(18Vで0.9W)。

低抵抗をダイオード順方向に差し替え、OFF化可能かみる。電源用ダイオードで80mA、小信号用ダイオードで70mAで正常動作、鮮かな音を感じる。 何か違いがあるかも知れない。2SJ377/2SK2231の小信号ダイオード順方向は、47mAだが大音量で歪。0.7VはやはりON電圧不足。赤色LEDでは正常音 だが90mAは過大。ダイオード2本直列は75mAで正常。我々は激しい貫通電流が存在すれば大抵は防げない雑音を生むのを知った。

(*) 最終段のBE間に入ったTrが最終段をONできたのは、前段のBE間ダイオードが逆耐圧付近でZD動作をした可能性がある。

(**) 2SA1359/2SC3422は、2SA1015/2SC1815など小信号用と同じく正面に向かって左からECB。他の2SA1887/2SC5000、2SA1931/2SC4881などのTrはBCE

であり、2SJ377/2SK2231もGDS、裏返しである。Trの(CE逆でなく)BE逆で動作らしきことをした理由は、もはや考えることもできない。

この回路では出力の無駄電圧は1段目のBE間電圧0.7Vに依存する。1段目をコンプリメンタリー・ソース・フォロア FETに代える可能性はある。ディプ レッションーエンハンスメント型FETは、GS間電圧0Vでドレイン電流を流して動作する。しかし、1段目による無駄電位削減は可能でも、2段目のVbeの 隠れる場所がなく無駄電圧を削減する目的を達しない。逆転ダーリントン接続CEFは、0.9V程度までが削減限界だろう。

ON/OFF負荷とZDを使ったCEG又はCSGは、無駄電圧をさらに削減する可能性があるが、その回路の動作がまだ十分成功していない。それよりは、2段型 CEFにおいて1段目のCEFを上述のGS間電圧0VのCSFにして無駄電圧を約1/2にして抵抗調節が要らないのがよい。なお、ここで元々少ない無駄電位を減 らすのは、それを1/2にすれば同じ熱設計で扱える出力電力が2倍になるからで、10Wのうち1Wが無駄の回路から、20Wのうち1Wがそうなる回路にしたい からである。電源18V〜24Vで1.4Vの無駄を上下に持つと18Vでは2.8V/18V*100%= 15.55%(24Vでは11.66%)の無駄が1段では18Vで7.77%(24V5.83%)になる。